基于遗传算法的组合电路BF故障Iddq诊断生成研究

2006/5/23 9:07:00

关键词:IDDQ;遗传算法;电路诊断生成 中图分类号:TN407 文献标识码:A An Algorithm Based on GA for Generating Diagnostic IDDQ Test Set for Bridging Faults ZHANG LanI, ZENG min2, XU hong-bin2 (1.ZTE,Zijinghua Road 68, Nanjing, Jiangsu 210012,China; 2. School of Automation Engineering, UESTC, Chengdu, Siehuan 610054, China) Abstract: This paper describes a diagnostic generation algorithm for Iddq. This algorithm is based on the GA, some effective technique, such as local - optimization procedure and levered generation, have been em ployed to improve the efficiency of the algorithm. Experimental results for large ISCAS85 benchmark circuits demonstrate its efficiency in comparison with results of previous methods. Key words: Genetic Algorithm; Diagnostic Generation 1 引言 电路的故障诊断包含故障检测和故障定位。电路的故障诊断在大规模集成电路的生产过程中具有重要意义。它有助于分析芯片模板上的各种缺陷从而最终提高芯片的产量和质量。故障诊断包括两种方法:物理检测方法和故障字典诊断方法。物理检测方法往往需要复杂的装备,甚至需要打开集成电路的封装损坏电路。故障字典诊断技术是基于故障字典项与实际故障响应的匹配来进行故障诊断。这种故障字典方法需要精确诊断生成技术来实现。

提交

查看更多评论

其他资讯

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

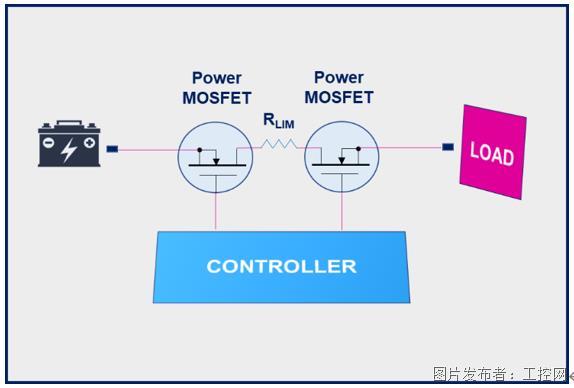

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议