低功耗器件的“设计时测试”方法

2007/2/7 9:02:00

在65nm制造工艺条件下,依靠电池供电的器件正在大量出现。这种先进的工艺技术使得新器件较前代工艺的同类器件具有很多改进。采用65nm工艺之后,设计人员可以在一块单独的裸片上集成远多于过去的晶体管,还可以在器件中集成多个IP内核、大量的嵌入式存储器、更多的复杂模拟电路,同时实现比90nm工艺下类似器件更高的性能、更低的功耗和更低的成本。 然而在65nm下,由于器件中晶体管漏电流造成的功耗却远高于(呈指数关系)旧工艺结点下的器件。因此,台积电(TSMC)之类的大型晶圆代工厂已经将减小漏电流当作65nm参考流程中的一个首要任务。泄漏并不是什么新现象,但65nm工艺器件的工作电压比老工艺器件的工作电压低,因此开启单个晶体管所需的阈值电压也比老工艺的器件低。阈值电压较低就可能经常无意中触发非活动的状态,从而导致源极到漏极流过很大的电流,或者说导致泄漏。用于解决这一问题的最新技术往往采用内建高Vt标头(header)或标尾(footer)的多阈值逻辑门,标头和标尾用于在空闲状态下关断逻辑门。此外,也可以在设计逻辑中添加一些特定的电源关断模式,而且设计师们也正在利用更多的门控时钟来管理设计中每个时钟区的功耗。以上各种方法综合起来,正在帮助我们减小晶体管的泄漏。 要想充分利用这些新技术,设计人员必须在整个设计流程中都非常关注功耗问题。硬件工程师和嵌入式软件工程师都必须尽早参与,以保证产品的设计成功和按时发布。同时,低功耗设计对设计验证,尤其是对所有电源管理特性的验证,也有很大影响。因为这需要在所有可能的工作条件下进行大量验证工作,包括测试每种功率模式。对所有功率模式(上电和掉电)以及随后的器件行为序列的测试必须在流片之前完成。此外,验证工程师还必须进行测试以保证孤立的逻辑也能正常工作。这是利用带随机和定向案例的广泛的测试套件实现的。 实现功耗相关特性的自动化验证是一次意义重大的努力,它要求设计人员在整个设计过程中都给予验证工作足够的重视。例如,低功耗逻辑测试套件必须确保专用逻辑不但能降低动态功耗,还能保证掉电的电路在任何工作状态下都不会向工作的电路传播随机数据。为确保这些问题不会发生,设计过程中每出现一次代码修改,验证工程师都必须进行大量仿真,并采用大量其他的格式验证资源。 低功耗可测试性设计面临的挑战 一个常被忽视,或者说设计人员最多在设计后期才会考虑的问题,是器件在制造测试过程中的功耗。在可测试性设计(DFT)中,尤其是低功耗器件的DFT中,需要考虑的问题很多。其中,尽早并且严格注意制造测试中的功耗,对于大量交付可靠的低功耗器件而言,十分关键。因为在制造测试过程中,器件的功耗如果大大超出器件的功率指标,可能会导致闸极氧化层击穿,严重时甚至会损坏芯片。 低功耗DFT的最佳方案需要采用一种“设计时测试”(Design With Test, DWT)流程,以便最好地解决标准的设计和实现流程中的测试问题,从而保证将这些问题带来的影响降至最小,并最终得到高质量的低功耗器件。DWT方法是指在整个设计流程中都采用同样的功耗感知测试策略,以便使每种工具都能注意到,尽量减小每一个低功耗测试步骤带来的影响,从而解决65nm低功耗器件制造中较难解决的测试问题。DWT方法将对功耗的关注深植入设计、实现和测试工具中,因而采用该方法后,可以将器件的功耗限制与时序、面积、良率和测试等其他约束条件联合起来,进行全面优化。 DWT助推低功耗DFT 采用DWT方法时,工具的集成深度以及不同工具之间是否具备流畅的互通性,决定了RTL验证、综合、测试、等效检验、区域规划以及布局和布线工具之间的功耗约束情况。全面优化的结果是使制造出的芯片可测性很高,并且器件不但在工作过程中,而且在制造流程的测试过程中都能够满足功耗预算。这种方法要求不论设计进行到流程的哪个阶段,都采用同一个文件定义功耗因素,从而保证整个流程中的所有工具对器件的功耗要求都有相同的理解。 要设计出高质量的低功耗器件,必须在整个设计过程中都给予DFT足够的重视。也就是说,DFT的范围必须扩展,其逻辑必须能在制造测试过程(包括晶元筛选、封装测试和环境审查)中以不超出器件功耗指标的方式控制和测试与功耗相关的电路。需要特别说明的是,在采用了DWT方法的低功耗设计中,可以轻易插入感知功耗的DFT结构,从而允许在整个芯片的功耗预算内对各个功耗区域进行测试。 一个器件中的裸片上往往分布有不同的孤立电压区。在制造测试中,这些电压区必须由扫入电源控制信号的数据来控制其开/关,而在芯片定型后要测试这多个电压区往往会导致功耗过大。低功耗测试中存在的挑战绝不仅仅是控制测试中的功耗。要在低功耗环境下达到高质量,那么各个分离单元、电平转换器和状态保持寄存器,只要需要测试,就必须能够通过一个扫描链控制。这样才可能测试如此复杂的结构,以保证在低功耗方面随机的、系统的甚至是微小的具体瑕疵都能被找到。 低功耗ATPG 在DWT流程的物理实现过程中,进行测试插入时是考虑了功耗的。测试插入包括将扫描链真正连接到边界扫描I/O、嵌入式存储器内建自测(BIST)控制器、片上压缩逻辑、片上时钟产生和IEEE1500封装。例如,在连接了片上测试压缩逻辑之后,会显著地增大功耗负荷。因此,插入片上压缩逻辑时必须进行功耗折衷。必须在全面理解功耗要求的情况下对扫描链的长度进行优化,以保证在与片上压缩逻辑有关的大量短扫描链间变化时产生的功耗不会对总功耗有负面影响。随着测试模式下的功耗情况越来越引人关注,在创建功耗优化的测试模式方面ATPG本身开始变得越来越重要。即通过限制开关行为,同时利用由设计师添加的功耗管理逻辑来达到限制功耗的目的。例如,感知功耗的ATPG就可以通过智能化填充扫描链中的“无需注意”位,将触发器的转换次数减至最少,从而达到极大减小功耗的目的。 最后一点,由于DWT的第一次测试肯定是在测试仪上运行,因而还能降低制造成本。这是因为DWT在测试和功耗验证间进行了相当紧密的集成。同时,在芯片流片之前进行制造测试的自动化验证(利用仿真、等效检验、约束产生和高级格式分析等技术)也使ATE程序能够一次成功。 本文小结 作为消费者,我们每天使用的产品中都有低功耗器件。此类器件能够持续兴旺发展的关键就是品质和可靠性,而不论品质还是可靠性都高度依赖于器件的制造测试工艺,以及能否通过制造测试剔除坏的器件,同时不因扫描测试时过大的功耗而降低器件的可靠性。保证低功耗环境下成功实现制造测试的最佳方法就是在设计早期就将利用能感知功耗的DFT和ATPG工具进行测试时的功耗考虑在内。而要使这些工具最大程度地发挥功效,测试就必须成为设计过程的一部分。于是,为保证低功耗产品的发展能够更进一步,“设计时测试”(DWT)这种对工具进行了深度集成并充分考虑测试过程中功耗的新方法就必将起到十分重要的作用。 信息来源于:汽车电子网

提交

查看更多评论

其他资讯

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

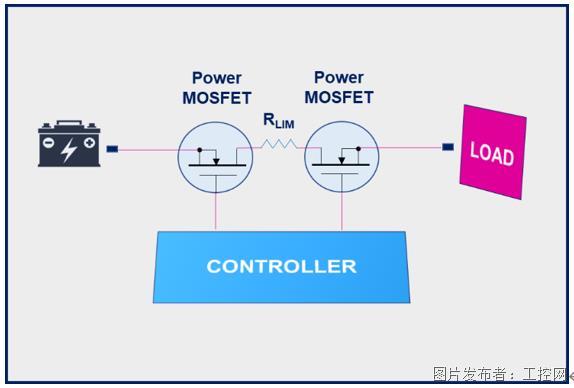

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议