基于PowerPC440GP型微控制器的嵌入式系统设计

2008/2/27 15:56:00

1 引言 PowerPC440GP是IBM公司推出的高性能32位RISC嵌入式处理器,片上集成了PowerPC440内核及各种丰富的外围设备接口资源,最高速度可达500 MHz,适合应用在嵌入式产品诸如交换机、路由器、网络服务器等台式设备中。本文针对该处理器的特点提出一种针对网络服务器的较为通用的应用系统设计方案,并对此方案的关键软硬件技术进行讨论。 2 PowerPC440GP的特点与性能 128位处理器局部总线(PLB)可提供峰值为4.2GB/s的读写能力,用来访问PCI,DDR SDRAM等高性能设备,采用36位地址路径,能提供64 GB内存寻址能力。 32位片上外围设备总线(0PB)连接串口、以太网口、外部总线控制器、I2C口等低性能设备,以提高PLB总线利用率。 10位寻址的DCR总线访问PLB总线上各种主从设备的状态与控制寄存器。 拥有64位片上双倍速率DDR SDRAM控制器,最多可提供4个设备片选信号。 拥有最高频率133MHz的64位PCI接口。 可支持8个外设的32位外部总线控制器。 2个10 MB/s/100 MB/s片上以太网控制器。 2个串口和2个I2C口。 32个通用输入输出口GPIO。 13个外部中断和45个内部中断资源。 CPU工作频率可在400 MHz、466 MHz、500MHz频率下通过初始化配置选择,一般功耗小于4W。 电源:逻辑电压为1.8 V,DDR SDRAM接口电压为2.5V,I/O口电压为3.3V。 3 应用系统设计方案 该网络服务器平台以PowerPC440GP为核心,进行了必要的扩展,系统结构框图如图1所示。

提交

查看更多评论

其他资讯

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

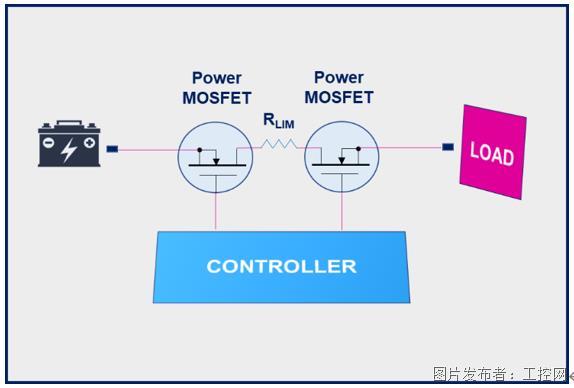

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议