Vortex86SX容错功能介绍

一. 关于容错性 容错是计算机应用系统稳定、可靠、有效、持续运行的重要保证。许多的服务行业必须保证二十四小时不间断运行,否则将给单位或企业带来很大的经济损失和社会负面影响,因此电脑的正常运行和数据的安全就显得尤为重要。电脑首要的也是最主要的安全问题就是硬件和软件的安全,但同时,由于PC机的安全性因素,基于该平台业务系统的安全,稳定可靠和系统的持续运行成为系统的关键,因此,x86架构下的容错系统受到越来越多的欢迎 。下面就结合我公司(昭营科技)的具体产品情况简单阐述Vortex86SX(以下简称VSX)的容错功能。 二. 容错原理图

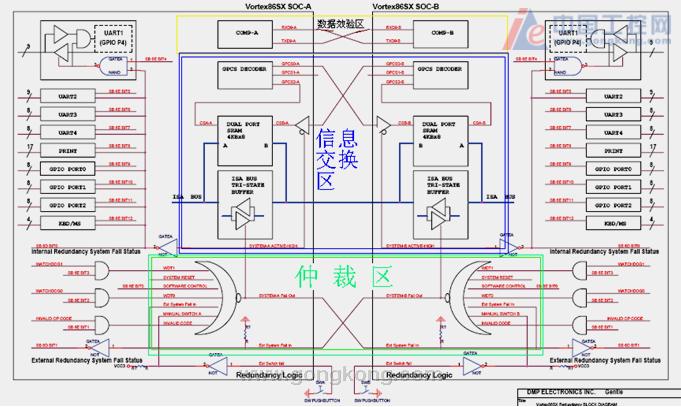

上图为我公司产品容错原理图,我们分为仲裁区、信息交换区、数据效验区和其他区域来讲解。

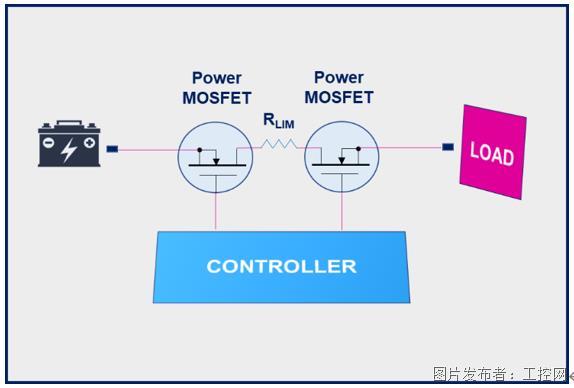

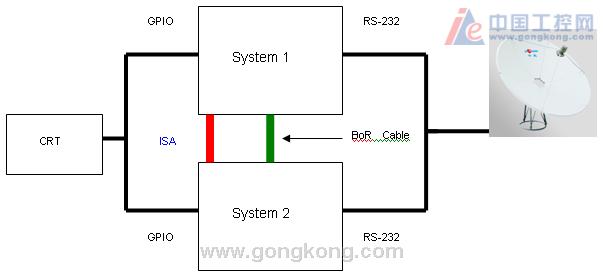

1、仲裁区: 是判断板卡在何种情况下让没M aster把控制权转给Slave。 A、WDT1:看门狗1启动 B、SYSTEM RESET:系统重新启动 C、SOFTWARE CONTRNOL:软件控制 D、WDT0:看门狗0启动 E、Ext system fail in:系统外在触发 F、MANUAL SWITCH A:系统手动切换 G、INVALID CODE:非法指令 在以上七种情况发生时M aster会把控制权推给Slave,因为转换时间极短仅为1微秒,达到即使板卡偶出现意外也不会死机,。 2、信息交换区: SRAM为暂存器有两个作用作为数据临时存放区域和共享空间实现数据的交换。在GPCS DECODER控制下M aster可以向自己的4K SRAM空间写数据,还可以通过GPCS0向Slave的4K空间写数据,这样不但使得M aster的存储空间扩大了一倍,从4K变为8K,而且更容易实现两块板卡信息的比较达到信息同步。 3、数据交换区: 通过高速串口COM9可以实现主从盘SRAM中数据的比对达到M aster和Slave信息的同步,也可以实现两个系统间的数据交换。 4、其它区域: UART1—UART4是串口数据的抑制容错,也就是两块主板(M aster and Slave)的串口同时接到设备的同一串口,M aster主板的串口会抑制Slave主板串口的工作,设备只接受M aster信息,所以串口是可控I/O。 GPIO PORT0----GPIO PORT2是指GPIO端口的抑制容错。 KBD/MS是指鼠标和键盘的抑制容错。 三. 容错的硬件设置 1. 必须有两块VSX CPU为核心的板卡,型号与规范一致每块板卡必须有PC104总线. 2. 把两块同样的VSX 板卡用104堆叠起来。 3. 用BoR 总线把两块板卡的容错接口连接起来。如下图

这样硬件就设置完成了。 四. 软件的设置 开机按DEL进入BIOS设置 选择Chipset下的 SouthBridge Configuration 目录如图

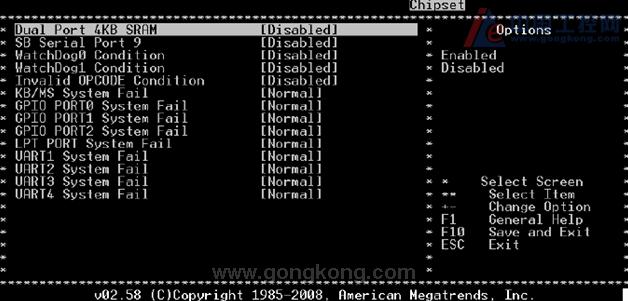

SouthBridge Configuration 目录下有GPCS configuration and Redundancy Control configuration 两项需要设置。 第一项:GPCS设置 1. 把GPCS功能打开设为[Enabled] 2. GPCS0 Command 来控制数据映射类型(内存映射与I/O映射),默认选择内存映射 8 bit 可读可写。 3. GPCS0 start address 设置数据映射起始地址,默认为[000c8000] 4. GPCS0 MASK compare bit 来确定有效字段数 第二项:Redundancy Control Configuration

1. a.. Dual port 4k SRAM 设置为 [Enabled] 打开4k SRAM 暂存器空间 b. SRAM Command来控制数据映射类型(内存映射与I/O映射),默认为[Mem r/w 8 bit] c. SRAM start Address设置数据映射起始地址,默认为[000D0000] d. SRAM Compare Bit来确定有效字段数,默认为[FFFFF000] 2. com9设置 a. SB serial port 9选择串口地址 b. IRQ9选择COM9中断地址 3.wachdog 0 and 1 看门狗容错功能的开启与关闭 4. Invalid opcode condition 非法指令容错功能的开启与关闭。 五. 关于容错涉及概念解释 1. 堆叠: 把两块VSX主板通过PC104接口叠加到一起。 2. BoR: BoR(bridge of redundancy),这是我公司专为容错性设计的一组总线,总线的两端分别连接到两块主板(A,B)的容错接口(Redundancy)线序如下图

A SYS | B SYS |

| 1 (GND) | 1 (GND) |

| 2 (SYSTEM-A Fail out) | 3 (Ext-SYSTEM Fail in) |

| 3 (Ext-SYSTEM Fail in) | 2 (SYSTEM-A Fail out) |

| 4 (GPCS0) | 5 SYS-GPCS-in |

| 5 SYS-GPCS-in | 4 (GPCS0) |

| 6 (TxD9) | 7 (RxD9) |

| 7 (RxD9) | 6 (TxD9) |

3. COM9 :在我公司板卡上还有个com9 在BIOS 中: Chipset→Southbridge Configuration →Redundancy Control Configuration 下 设置端口地址与中断号,COM9可以作为中两个系统信息的比对,保持主从板卡信息同步,当然您还可以把com9作为一个高速串口用用于两个板卡间任意信息的传送。 如图所示: 4. 可控与非可控 所谓可控I/O 是指同一个I/O被两个设备共同使用,主机为工作机有控制I/O权,从只是追随主在跑并不参与控制 。 常用可控I/O有:串口,并口,GPIO,键盘鼠标。 非可控I/O有:USB ,网口,LCD……………. 六. 容错理论的测试 1. 对寄存器地址6DH的测试,通过寄存器地址6DH数据的读取判断系统为M aster or Slave ,你可以用软件读取6DH的值(00000010为主M aster, 00000001 为从Slave)来判断主从主板。 2. 在debug 模式下通过对SRAM地址值的读写来判断主从盘,在M aster的系统上可以访问Slave系统的SRAM空间,访问(读/写)的方式可以在BIOS中设定,而SLAVE系统不可以访问M aster系统的SRAM。因为M aster有主控权而Slave没有。 七. 应用典型案例分析

上图为某一航空司地面控制台,当主机开启power按下,两片VSX-6154主板同时启动,按照时间先后随机决定一个为M aster,另一个为Slave。M aster拥有主控权并抑制Slave的各项功能,所以显示器显示M aster内容,Slave只是跟着M aster跑。M astert收到信息把信息传递到显示器上,同时通过BoR总线完成与slave的信息比对,达到信息的同步。如果M aster因为意外而重启,这时M aster在死机的一瞬间把控制权推向Slave,Slave接过M aster的信号就变成了M aster,将继续运行。原M aster通过重启或者修复后就失去了控制权力变成跟着新的Slave,等到有时机再次接手M aster的工作。 控制室在监测飞机状况后指挥人员指导飞机有次序的飞行,起飞和降落,这时突然M aster由于意外重新启动,Slave立即接手主的工作,采集雷达信息并在显示器上显示,M aster在重启完成后,变成Slave,原来的M aster变成了Slave,通过COM9读取主的信息,与主信息达到同步,时刻准备着接手主的工作,而发生的这一切在控制台前指挥的人员并不知道。如果只有一块主板,那么所发生的一切就可想而知了。 八.综上所述, Vortex86SX容错功能实现非常简单,且功能强大。它主要有以下几大特点: M aster/Slave主板谐调工作 可诊断六种不可预知的系统死机故障 M aster/Slave主板可在1 us(10的负6次方秒)内转换 可抑制Slave主板下的ISA总线 可编程抑制Slave主板的I/O端口(在BIOS中设置) 设计高速串口作M aster/Slave主板间的数据传输 M aster/Slave主板各提供4KB SRAM作数据交换与备份 支持系统死机计数

提交

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议