AD9847的原理及其在CCD 成像系统中的应用

随着晶圆工艺的不断发展,CCD相机和摄像机的发展也趋于小型化、智能化、功能多样化。随着45 nm甚至40 nm技术的发展,无论是消费级还是科学级摄像机,设计师们在设计时更愿意选择小型且功能强大的芯片。ADI公司推出的业界通用AFE已经配置于多种知名的高性能数码相机和数码摄像机,凭借这种技术专长,ADI现已能够为用于高端数码相机、数码摄像机以及高性能科学和工业图像处理应用(例如,机器视觉、生物医学图像处理和碰撞测试分析)的互补金属氧化物半导体(CMOS)和电荷耦合器件(CCD)图像传感器提供专业的AFE数据转换器。

1 CCD成像系统组成

CCD成像系统设计领域较多,包括光学系统、机械系统、电源供电系统、CCD驱动电路系统、状态控制系统及图像数据处理系统等[1]。本系统框图如图1,其中光学镜头部分没有标出。系统处理流程为:CCD在驱动信号控制下,将经由光学镜头透过的光信号变换为电信号,即模拟视频信号。视频信号分为左右两边经两路AD9847进行模数转换,转换后数字信号送入FPGA进行一系列处理最终送至终端。系统中FPGA采用XILINX公司的XC4VLX25。一般FPGA处理后的信号根据终端的不同而相应地给出标准信号以便进行图像显示。该系统中终端为高清监视器,故最终接口为HDSDI接口。

AD9847在系统中需与FPGA联合工作。因AD9847集成TD(Timing Driver),所以可以为CCD提供垂直驱动信号、复位信号、箝位信号及消隐信号。系统中CCD采用柯达KAI-2093[2],最高工作频率为40 MHz,系统工作频率为37.125 MHz,RG信号的窄脉冲达到200 MHz高频;FPGA是系统中的核心器件,如果以上信号都由FPGA提供,则对FPGA有很高的性能要求,故采用驱动信号由AD9847与FPGA联合提供的方式工作。AD9847的加入使得成像系统体积减小、操作简便。AD9847不同于其他AFE的地方就是它除了可以对视频信号进行相应处理外还,可以为CCD提供足够驱动能力的驱动信号,最高可达24.5 mA。

2 AD9847的介绍

2.1 主要特点

AD9847是美国ADI公司的一款面向CCD的、完善的低功耗单通道模拟信号处理器。AD9847可以工作在三种模式下,对面阵CCD信号、模拟视频信号和普通的交流信号进行A/D转换。AD9847以其高精度、高速度的模数转换能力,及其所具有的完善的性能结构,广泛应用在工业控制、医疗仪器、科学研究等领域的高精度图像采集系统中[3]。

AD9847的主要特征:

(1)10 bit、40 MHz的A/D转换器;

(2)40 MHz相关双采样(CDS);

(3)-2 dB~+10 dB像素增益放大器(PxGA);

(4)2 dB~+36 dB,10 bit可变增益放大器(VGA);

(5)低噪声可变增益控制的箝位电路;

(6)模拟视频信号预息影功能;

(7)精准的时钟核,40 MS/s时的分辨率为500 ps;

(8)3线串行接口配置;

(9)片上时序发生器,可在外部同步信号的作用下给CCD芯片提供所需的时序信号(H1,H2,RG),配合另外提供的V、VSUB信号,可以驱动CCD工作;

(10)48脚LQFP封装,大大节省电路板空间。

2.2 AD9847的工作原理

AD9847在基准信号VD、HD、CLI 作用下,通过FPGA对三线串口进行编程,为系统设置适当的寄存器配置。AD9847各个功能的实现建立在内部寄存器正确配置的基础上。三线串口为SLOAD、SCLOCK、SDATA,共有两种配置方式:一种是串行写操作,连续写入8位地址信号和6位数据信号,SLOAD信号在写入数据期间一直处于低电平状态,在此期间SCLOCK信号表现为时钟信号,其他时间维持高电平,SDATA的数据在SCLOCK的时钟上升沿被锁存;另一种是连续的串行写操作,只有一个8 bit地址位作为首地址,后面依次为以6 bit为一组的数据位,每6 bit对应一个地址,地址以首地址为基准依次递增,最终将数据写进对应的寄存器,SLOAD在此期间一直为低,直到最后一个寄存器被装载。AD9847的配置主要是完成对CDS采样信号的置位、驱动信号波形、可变增益放大器的增益、钳位电平以及其他功能等的设置。AD9847基本工作流程为CCD模拟视频信号经过射随器之后送给AD9847,在AD9847内部首先经CDS进行相关双采样,消除噪声干扰,然后通过增益放大再送至ADC进行A/D转换,最终将转换后的数字信号送至下一步电路进行处理。DOUTPHASE寄存器可以设置输出数字信号的最佳位置。

3 AD9847在成像系统中的应用

3.1 寄存器配置

该系统中AD9847与FPGA作为核心,FPGA作为AD9847的上位机控制AD9847 的工作。AD9847作为AFE又有着无法替代的优势,它将很多视频信号处理电路集成起来替代了很多复杂的分电路。系统中AD9847和FPGA由同步时钟控制,上电初始化后FPGA经三线串口配置AD9847。AD9847共有164个寄存器,有些寄存器为双宽度寄存器,占有两个地址,对于这样的寄存器必须两个地址都写入数据才能使其作用。对于寄存器中有些数据位宽不足6 bit的,在配置时需补足6 bit。大部分寄存器地址是连续的,仅有一些不连续。根据参考文献[3]中要求的AD9847寄存器配置的顺序,有些地址偏后的寄存器可能需要先配置,这样就导致有些寄存器只能采用串行写操作模式,对于地址连续的寄存器可采用连续的串行写操作模式。故在对AD9847寄存器配置过程中,将串行写操作模式和连续串行写操作模式结合起来,只需注意每个bit数据与SCLOCK对应位置即可。

3.2 驱动电路

系统工作首先需要驱动CCD,为减轻FPGA的负担,AD9847承担产生一部分驱动信号的任务。HBLK、H1-H4、RG等相关寄存器可产生所需要的驱动信号。对垂直时钟H1行空白期间电平极性应当设置为低,因为后续的电压转换电路中对其进行了反相,参考文献[2]中H1信号波形图。由FPGA产生的水平转移驱动信号配合AD9847产生的驱动信号经由电压转换电路驱动CCD工作。CCD在驱动信号作用下,输出模拟视频信号如图2。图中,1通道为CCD视频信号,4通道为H1信号。

3.3 相关双采样

视频信号在AD9847内部首先经内部相关双采样电路对每个CCD像素信号进行两次采样,以提取视频信息和抑制低频噪声。由于CCD每个像素的输出信号中既包含有光敏信号,也包含有复位脉冲电压信号,若在光电信号的积分开始时和积分结束时,分别对输出信号采样,并且使得两次采样的间隔时间远小于时间常数RonC(Ron为复位管的导通电阻),则这样两次采样的噪声电压相差无几,而这两次采样的时间又是相关的[4]。若将两次采样值相减,就基本消除了复位噪声的干扰,得到信号电平的实际有效幅值。通过设置SHPPOSLOC和SHDPOSLOC寄存器来决定SHP和SHD的采样位置,SHP采样参考电平,SHD采样有效电平,采样位置的设定是得到好的CCD信号的关键。因AD9847的SHP、SHD均在内部产生,外部并没有输出管脚,故无法用示波器显示采样信号。相关双采样时序如图3所示。

3.4 箝位及增益放大电路

经CDS处理的CCD信号送至下一个电路。箝位电路用来消除信号链中的残留偏压,并且跟踪CCD暗像素的频率成份,错误的信号将被过滤掉,所以噪声降低,去掉偏压还可减小对增益改变的影响。AD9847内部箝位信号为CLPDM、CLPOB,箝位位置通过配置寄存器来改变。具体的寄存器配置内容需根据AD9847 datasheet和CCD的datasheet的要求进行配置,只需根据CCD行转移信号找出black pixel、effective pixel的位置即可。

AD9847的增益放大器有PxGA(像素增益放大器)和VGA(可变增益放大器),两个增益放大器共同工作,对弱信号放大、强信号缩小,使图像灰度处于比较理想的状态。其中,PxGA为单个的彩色像素提供单独的增益调整。一个可编程增益放大器有4个单独值,PxGA可将增益值分配给单个像素。PxGA可以用于白平衡调整彩色信号,可减少后续的数字处理工作量,并很方便地为CCD摄像机系统提供了白平衡功能。配置ctlmode寄存器可以选择PxGA的工作模式,ctlmode可针对不同类型的CCD彩色滤波阵列设置7种不同的彩色引导模

提交

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

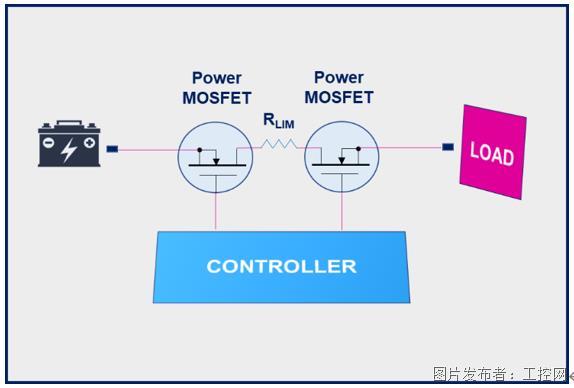

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议