灵巧划分在WiMAX射频中的应用 (2)

2010/3/11 9:45:00

对于现有工艺,混合信号ASIC 设计成本比纯数字ASIC 高,增加成本的原因有以下五个 主要方面:

1. 对于一种特定的工艺,混合信号器件的制造工艺的成本本来就很高。混合信号工艺的特点是需要额外的处理步骤,例如更厚的氧化层、低门限器件和额外的注入。通常, 混合信号的晶圆成本要比纯数字晶圆的成本要高20%。

2. 制造工厂需要投入大量资金以降低缺陷密度,从而获得接近97%~98%的高良率,这些 都取决于裸片面积。另一方面,模拟电路IC 的良率与设计本身有关。为了在对功耗指 标做出折衷的条件下实现规定的性能,与数字设计相比,模拟电路的设计要在工艺变化范围窄的情况下达到技术指标的要求,这就导致其良率受参数限制,从而增加了混合信 号设计成本。这方面将使混合信号设计成本增加了10%以上。

3. 从数字调制解调器中去除模拟功能单元可以简化生产测试的开发,并且对节省生产测试时间有所帮助。采用数字通用测试仪替代昂贵的混合信号测试仪可以把测试成本降 低15%~20%。

4. 测试覆盖率工具允许数字设计工程师建立故障覆盖率扫描链,从而简化生产测试。然而,混合信号测试需要在几微伏范围内测量各种模拟技术指标。混合信号设计需要的 测试时间至少是纯数字电路设计的五倍。在测试仪上并行处理可以缩短测试时间。假设 采用一种积极的测试程序方法——混合信号器件的测试成本将会提高两到三倍。

5. 集成的数据转换器内核通常是由具有相关版权和/或一次性工程费用(NRE)的第三方 和/或内部机构开发的知识产权。与纯数字ASIC 解决方案的设计工具套件相比,混合信 号设计所采用的设计和支持工具也是一笔附加投资。设计新的混合信号ASIC 所需要的 一套开发工具比纯数字ASIC 所用工具要多50 万美元以上。

此外,模拟电路不会像数字电路那样随着工艺线宽的缩小而成比例缩小。图4 所示,混 合信号IC 的成本会随着特征尺寸的减小而增加。图中将成本曲线相对180nm 纯数字ASIC 的成本做了归一化处理。历史上,数字ASIC 工艺特征尺寸每次从一代演进到下一代, 其成本都会随之降低三分之一。与此相反,混合信号IC 的成本随着混合信号裸片面积 的减小反而增加。这是因为存在这样一个事实,即受噪声限制的模拟电路的成本不随光 刻工艺线宽的减小而降低,而数字电路的成本会随着工艺线宽减小呈平方关系降低。

新工艺设备投资和制造工艺复杂度的增加导致每平方毫米的裸片成本出现一代比一代净增长的趋势。而数字电路的工艺尺寸成比例降低使每只晶体管的成本进一步降低。因 为模拟电路的成本并不随着工艺尺寸减小而成比例地减小,所以混合信号产品总体成本 开始时保持平稳,后来却随着工艺尺寸的减小而增大。 在大规模产品市场中,企业必须满足市场定价要求的同时保持价格竞争力,从而为投资者提供合理回报。

如果一家公司的成本是一流竞争对手的两倍时,就必须迅速采取新的 手段或新的策略。尽管与混合信号设计相关的所有挑战仍将继续存在,但灵巧电路划分 的众多好处中也包括利用并不总是适合于模拟/RF 电路的摩尔定律的所有优点来显著地 降低系统成本。除了每个器件成本的增加,没有选择最优工艺和较长的投放市场时间的机会成本都注定 会影响项目的投资回报。准备就绪的模拟和混合信号内核的可用性要比数字工艺晚大约 两年,或者差不多有一代的差距,而用于批量生产的内核要达到可用性大约需要四年时 间,而灵巧划分方法可以使系统供应商根据其需要选择最优化工艺,而不受经过认证的 模拟内核的可用性约束。

机会成本与非最优化工艺的选择关系很大。例如,在宽带无线 领域,制造商已经发布了90nm 的内核设计。90nm 数字SoC 设计和130nm 的产品之间的 成本差距竟高达200%以上!而对于65nm 的内核设计,成本差距可能高达多倍。 这里推荐的划分方法提供了一种将节省下来的时间和资源重点用到开发下一代产品的机会——从而可能研发出比竞争对手超前一代的产品投放市场,因为他们把有价值的资源耗费在解决混合信号ASIC 设计的固有难题上。

向数字射频基带接口转移带来的性能优势

灵巧划分凭借在开发、支持和单位成本方面的成本优势能够提供高性能的系统解决方案。 对于具有高峰均比的OFDM 系统来说,在RF 器件上实现的高线性度以及在数字基带(DBB) 上的先进同步和信道估计算法绝不能因受ADC 和DAC 的动态范围的限制而作出折衷。

在 存在噪声、信道衰落和干扰条件下,为了实现更好的性能,必须仔细考虑对裕量的管理。随着对AGC 环路的集成,ADC 的动态范围能够与RF 前端的能力相匹配,从而使像64QAM 这样高的数据速率成为可能。因为DBB 与RF 芯片之间存在复杂的相互影响,所以许多供应商都在努力推出它们的参考设计。

另外,他们利用像符号到符号AGC 这样的先进技 术来改进移动环境中常见的系统的信道衰落性能。与分立式AGC 环路(例如,用两颗独 立芯片实现AGC 算法)不同,这里推荐的灵巧划分能够实现快速的AGC 收敛,从而使DBB 可以将更多时间用于信道估计和同步,从而把系统的性能改善许多个分贝,相当于进一 步提高了系统的动态范围和传输速率。

为了消除来自相邻或相邻信道的信号干扰,需要采取滤波措施。为了解决这个问题,必须在滤波器的线性度和复杂度之间做出谨慎的折衷。对于低成本零中频(ZIF)体系结构, 使用数字滤波器可以实现最终的信道选择性。滤波电路如同增益电路,必须分布在RF 和后续数字滤波器之间。

灵巧划分能够最优化模拟滤波和数字滤波之间的滤波要求,从 而充分利用ADC 的动态范围。 功耗也是移动系统的一项重要参数。数字芯片的功耗直接与电源电压的平方和栅极电容成正比。因此,对于从130nm 向90nm 的工艺的转移可以节省8 倍的功率。而对于利用 灵巧划分方法的DBB,在130nm 工艺上功耗为1W~1.5W;当升级到90nm 工艺时,其功耗 大幅度减低到200mW。

本文小结

数字革命已经实现了利用精细线宽工艺集成百万门级电路的解决方案。这些SoC 解决方 案开发成本昂贵,并且投资回报压力巨大。为了取得成功,人们必须选择合适的市场,重点放在提高核心竞争力以低成本并及时地提供差异化的产品。为了把风险降到最小而 相互合作并按照统一的计划表工作是极具吸引力的选择。

“从RF 到数字”的射频系统的灵巧划分提供了取得成功的四项关键因素——高性能解 决方案,把重点放在提高核心竞争力上,把功耗降到最小及最快的投放市场时间。

合适的模拟和数字功能划分解决了许多与在数字ASIC 上集成模拟电路相关的问题,从 而进一步加快了产品的投放市场时间并且延长了其在市场中的生存时间。它能够最优化 系统以实现高性能。 对于拥有数字调制解调器和媒体访问控制器专门经验的数字基带芯片供应商来说,灵巧划分可以使他们把关键资源集中于能够进一步提高产品价值的任务和项目上。

对于大规模生产应用,工艺的选择是至关重要的。快速转向较新工艺的能力可以产生新的成本和性能点,从而带来竞争优势。灵巧划分方法正在被ADI 公司多种标准产品制造 部门所采纳,如移动手机的Digi-RF 事业部,针对WLAN 和WiMAX 应用的JC-61 事业部 及各种专用系统中的应用。ADI 公司提供的ADI/Q 接口允许轻松地实现这种成本——性能优化策略。

1. 对于一种特定的工艺,混合信号器件的制造工艺的成本本来就很高。混合信号工艺的特点是需要额外的处理步骤,例如更厚的氧化层、低门限器件和额外的注入。通常, 混合信号的晶圆成本要比纯数字晶圆的成本要高20%。

2. 制造工厂需要投入大量资金以降低缺陷密度,从而获得接近97%~98%的高良率,这些 都取决于裸片面积。另一方面,模拟电路IC 的良率与设计本身有关。为了在对功耗指 标做出折衷的条件下实现规定的性能,与数字设计相比,模拟电路的设计要在工艺变化范围窄的情况下达到技术指标的要求,这就导致其良率受参数限制,从而增加了混合信 号设计成本。这方面将使混合信号设计成本增加了10%以上。

3. 从数字调制解调器中去除模拟功能单元可以简化生产测试的开发,并且对节省生产测试时间有所帮助。采用数字通用测试仪替代昂贵的混合信号测试仪可以把测试成本降 低15%~20%。

4. 测试覆盖率工具允许数字设计工程师建立故障覆盖率扫描链,从而简化生产测试。然而,混合信号测试需要在几微伏范围内测量各种模拟技术指标。混合信号设计需要的 测试时间至少是纯数字电路设计的五倍。在测试仪上并行处理可以缩短测试时间。假设 采用一种积极的测试程序方法——混合信号器件的测试成本将会提高两到三倍。

5. 集成的数据转换器内核通常是由具有相关版权和/或一次性工程费用(NRE)的第三方 和/或内部机构开发的知识产权。与纯数字ASIC 解决方案的设计工具套件相比,混合信 号设计所采用的设计和支持工具也是一笔附加投资。设计新的混合信号ASIC 所需要的 一套开发工具比纯数字ASIC 所用工具要多50 万美元以上。

此外,模拟电路不会像数字电路那样随着工艺线宽的缩小而成比例缩小。图4 所示,混 合信号IC 的成本会随着特征尺寸的减小而增加。图中将成本曲线相对180nm 纯数字ASIC 的成本做了归一化处理。历史上,数字ASIC 工艺特征尺寸每次从一代演进到下一代, 其成本都会随之降低三分之一。与此相反,混合信号IC 的成本随着混合信号裸片面积 的减小反而增加。这是因为存在这样一个事实,即受噪声限制的模拟电路的成本不随光 刻工艺线宽的减小而降低,而数字电路的成本会随着工艺线宽减小呈平方关系降低。

新工艺设备投资和制造工艺复杂度的增加导致每平方毫米的裸片成本出现一代比一代净增长的趋势。而数字电路的工艺尺寸成比例降低使每只晶体管的成本进一步降低。因 为模拟电路的成本并不随着工艺尺寸减小而成比例地减小,所以混合信号产品总体成本 开始时保持平稳,后来却随着工艺尺寸的减小而增大。 在大规模产品市场中,企业必须满足市场定价要求的同时保持价格竞争力,从而为投资者提供合理回报。

如果一家公司的成本是一流竞争对手的两倍时,就必须迅速采取新的 手段或新的策略。尽管与混合信号设计相关的所有挑战仍将继续存在,但灵巧电路划分 的众多好处中也包括利用并不总是适合于模拟/RF 电路的摩尔定律的所有优点来显著地 降低系统成本。除了每个器件成本的增加,没有选择最优工艺和较长的投放市场时间的机会成本都注定 会影响项目的投资回报。准备就绪的模拟和混合信号内核的可用性要比数字工艺晚大约 两年,或者差不多有一代的差距,而用于批量生产的内核要达到可用性大约需要四年时 间,而灵巧划分方法可以使系统供应商根据其需要选择最优化工艺,而不受经过认证的 模拟内核的可用性约束。

机会成本与非最优化工艺的选择关系很大。例如,在宽带无线 领域,制造商已经发布了90nm 的内核设计。90nm 数字SoC 设计和130nm 的产品之间的 成本差距竟高达200%以上!而对于65nm 的内核设计,成本差距可能高达多倍。 这里推荐的划分方法提供了一种将节省下来的时间和资源重点用到开发下一代产品的机会——从而可能研发出比竞争对手超前一代的产品投放市场,因为他们把有价值的资源耗费在解决混合信号ASIC 设计的固有难题上。

向数字射频基带接口转移带来的性能优势

灵巧划分凭借在开发、支持和单位成本方面的成本优势能够提供高性能的系统解决方案。 对于具有高峰均比的OFDM 系统来说,在RF 器件上实现的高线性度以及在数字基带(DBB) 上的先进同步和信道估计算法绝不能因受ADC 和DAC 的动态范围的限制而作出折衷。

在 存在噪声、信道衰落和干扰条件下,为了实现更好的性能,必须仔细考虑对裕量的管理。随着对AGC 环路的集成,ADC 的动态范围能够与RF 前端的能力相匹配,从而使像64QAM 这样高的数据速率成为可能。因为DBB 与RF 芯片之间存在复杂的相互影响,所以许多供应商都在努力推出它们的参考设计。

另外,他们利用像符号到符号AGC 这样的先进技 术来改进移动环境中常见的系统的信道衰落性能。与分立式AGC 环路(例如,用两颗独 立芯片实现AGC 算法)不同,这里推荐的灵巧划分能够实现快速的AGC 收敛,从而使DBB 可以将更多时间用于信道估计和同步,从而把系统的性能改善许多个分贝,相当于进一 步提高了系统的动态范围和传输速率。

为了消除来自相邻或相邻信道的信号干扰,需要采取滤波措施。为了解决这个问题,必须在滤波器的线性度和复杂度之间做出谨慎的折衷。对于低成本零中频(ZIF)体系结构, 使用数字滤波器可以实现最终的信道选择性。滤波电路如同增益电路,必须分布在RF 和后续数字滤波器之间。

灵巧划分能够最优化模拟滤波和数字滤波之间的滤波要求,从 而充分利用ADC 的动态范围。 功耗也是移动系统的一项重要参数。数字芯片的功耗直接与电源电压的平方和栅极电容成正比。因此,对于从130nm 向90nm 的工艺的转移可以节省8 倍的功率。而对于利用 灵巧划分方法的DBB,在130nm 工艺上功耗为1W~1.5W;当升级到90nm 工艺时,其功耗 大幅度减低到200mW。

本文小结

数字革命已经实现了利用精细线宽工艺集成百万门级电路的解决方案。这些SoC 解决方 案开发成本昂贵,并且投资回报压力巨大。为了取得成功,人们必须选择合适的市场,重点放在提高核心竞争力以低成本并及时地提供差异化的产品。为了把风险降到最小而 相互合作并按照统一的计划表工作是极具吸引力的选择。

“从RF 到数字”的射频系统的灵巧划分提供了取得成功的四项关键因素——高性能解 决方案,把重点放在提高核心竞争力上,把功耗降到最小及最快的投放市场时间。

合适的模拟和数字功能划分解决了许多与在数字ASIC 上集成模拟电路相关的问题,从 而进一步加快了产品的投放市场时间并且延长了其在市场中的生存时间。它能够最优化 系统以实现高性能。 对于拥有数字调制解调器和媒体访问控制器专门经验的数字基带芯片供应商来说,灵巧划分可以使他们把关键资源集中于能够进一步提高产品价值的任务和项目上。

对于大规模生产应用,工艺的选择是至关重要的。快速转向较新工艺的能力可以产生新的成本和性能点,从而带来竞争优势。灵巧划分方法正在被ADI 公司多种标准产品制造 部门所采纳,如移动手机的Digi-RF 事业部,针对WLAN 和WiMAX 应用的JC-61 事业部 及各种专用系统中的应用。ADI 公司提供的ADI/Q 接口允许轻松地实现这种成本——性能优化策略。

提交

查看更多评论

其他资讯

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

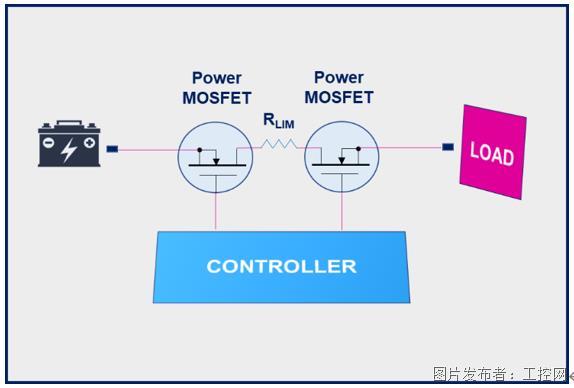

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议