基于FPGA的数字电视信号发生器的设计与实现 (2)

数字输出部分由驱动电路与接口芯片组成,

2.2.4 人机界面与控制单元

控制模拟信号输出类型,并通过输出I2C总线对D/A转换芯片的寄存器进行相应配置。根据外部输入信号,产生相应的图案/格式选择信号和配置芯片选择信号,控制主芯片与配置芯片的断电与上电时序,与选择连接开关模块共同完成测试图切换功能。这种单片多配置方案,信号转换速度很快,与单片单配置方案一样,为毫秒级。

2.3 FPGA测试图像信号产生

综合测试图像信号实际上是由多种测试信号合成的,包括圆信号、棋盘信号、多波群信号、彩条信号等。设计将综合测试图分为三个层次实现。第一层设计采用圆信号作为选通信号,圆信号外的视频有效区域输出棋盘信号,而圆信号内的视频有效区域输出多种测试信号;第二层设计采用行计数器值作为信号划分边界值,不同的行域输出不同的测试信号,用于测试设备的各种性能;第三层设计采用像素计数器值作为信号内部的区域划分参数,完成每种测试信号的生成。其代码设计基本框图如图4所示。

其中圆外的棋盘信号采用灰底白格棋盘,圆内信号从上至下依次设计为白场、信号、2T脉冲信号、黑白场交织信号、100%彩条信号、亮度多波群信号、6电平亮度五阶梯信号、2T脉冲信号与色亮时延差观察信号。其中黑白场交织信号中黑场与白场交替出现,每场宽80个像素点;彩条信号电平符合 100/0/100/0,每个彩条信号宽160个像素点;亮度多波群信号每波带信号宽160个像素点;6电平亮度五阶梯信号每阶梯宽160个像素点;2T 脉冲信号为半幅值宽度为34 ns、幅度为80%视频幅度的2T正弦平方正脉冲和负脉冲信号;根据黄、红色亮度电平相差较大及便于观察等因素,色亮时延差观察信号采用黄、红信号,其红黄交界处与其上面的2T脉冲峰值点在测试图中的水平方向位置相一致。为有效利用FPGA资源,并缩短开发周期,综合测试图中的多波群信号直接调用ROM的 IP核实现。

3 结 语

基于FPGA的数字电视信号发生器体积小,携带方便,能生成了综合测试图、SMPTE RP 219-2002彩条测试图等复杂信号,可全面地评估数字电视系统或设备的基本质量,特别适合用于电视台(数字节目)播出前对系统或设备进行测试评价及接收、显示设备的调整,同时也适合电视台其他技术部门以及数字电视设备生产流水线上或维修部门等用于对系统或设备进行调整和检测;另外还可以借助选行视频测试仪对系统或设备进行

提交

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

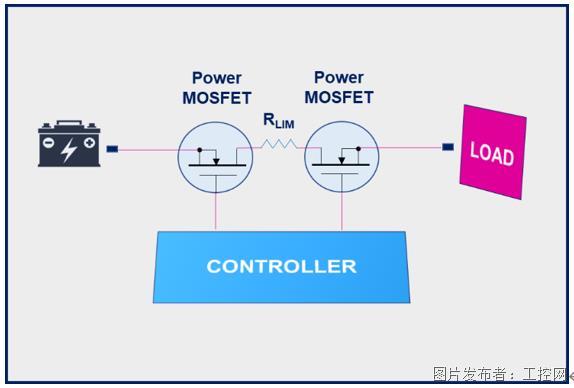

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议