PXI平台与高速量测模块同步研究

前言 随着电子制造技术的日益发展,集成电路的功能变得越来越复杂,而体积却越来越小,因此对制造测试电子元件的厂商而言,如何以最快的时间建造出最具竞争力的测试平台,的确是一门不小的学问。 1960年代末期,Hewlett-Packard设计出了所谓的HP-IB(Hewlett- Packard Interface Bus)作为独立仪器与计算机之间的沟通通道。由于其高速的数据传输率(对当时而言),很快便广为大家所接受,因此后来IEEE便将此接口更名为GPIB(General Purpose Interface Bus)。然而为了应付更为复杂的测试环境与挑战,GPIB便显得捉襟见肘。1987年VXI协会成立,并制订了所谓instrument-on-a-card的标准,也就是 VXI (VMEbus eXtensions for Instrumentation)。VXI以其模块化而且坚固的架构,的确为量测与自动化产业带来不少的好处。 近十年来,随着个人计算机的剧烈革命与普及,以PCI Bus为架构的仪器模块大为发展。因此1998年 PXI System Alliance(PXISA)成立,让PXI(PCI eXtensions for Instrumentation)成为一个开放的标准架构。PXI的平台不仅具有类似VXI的开放架构与坚固的机构外型,更由于其设计了一连串适合仪器开发所用的同步信号,而使得PXI更适合作为量测与测试自动化的平台。 本文主要目的是介绍在PXI平台下,如何利用PXI的优点,进行量测仪器模块之间精密而且快速的同步动作。内容包含PXI的简介与说明、量测仪器模块常用的同步信号以及应用实例。 PXI简介 测试系统制造商的工程师会问,什么是PXI?以PXI的仪器模块和PXI系统做开发平台会有什么好处?和CompactPCI或PCI有哪些不同?首先,我们想利用PXI平台作为量测仪器的平台,那么就得先知道PXI平台的架构与其优点,这样才能与仪器模块配合,发挥出最大的效益。 简单来说,PXI是以PCI(Peripheral Component Interconnect)及CompactPCI为基础再加上一些PXI特有的信号组合而成的一个架构。PXI继承了PCI的电气信号,使得PXI拥有如PCI bus的极高传输数据的能力,因此能够有高达 132Mbyte/s到528Mbyte/s的传输性能,在软件上是完全兼容的。另一方面,PXI采用和CompactPCI一样的机械外型结构,因此也能同样享有高密度、坚固外壳及高性能连接器的特性。PXI与CompactPCI相互关系如图一所示。

一个PXI系统由几项组件所组成,包含了一个机箱、一个PXI背板(backplane)、系统控制器(System controller module)以及数个外设模块(Peripheral modules)。在此以一个高度为3U的八槽PXI系统为例,如图二所示。系统控制器,也就是CPU模块,位于机箱的左边第一槽,其左方预留了三个扩充槽位给系统控制器使用,以便插入因功能复杂而体积较大的系统卡。由第二槽开始至第八槽称为外设槽,可以让用户依照本身的需求而插上不同的仪器模块。其中第二槽又可称为星形触发控制器槽(Star Trigger Controller Slot),其特殊的功能将于后面的文章中说明。

一个PXI系统由几项组件所组成,包含了一个机箱、一个PXI背板(backplane)、系统控制器(System controller module)以及数个外设模块(Peripheral modules)。在此以一个高度为3U的八槽PXI系统为例,如图二所示。系统控制器,也就是CPU模块,位于机箱的左边第一槽,其左方预留了三个扩充槽位给系统控制器使用,以便插入因功能复杂而体积较大的系统卡。由第二槽开始至第八槽称为外设槽,可以让用户依照本身的需求而插上不同的仪器模块。其中第二槽又可称为星形触发控制器槽(Star Trigger Controller Slot),其特殊的功能将于后面的文章中说明。

图二 典型3U高度的PXI系统架构。背板上的P1接插件上有32-bit PCI信号,P2接插件上则有64-bit PCI信号以及PXI特殊信号。那么前面所说的PXI特有的信号又是什么呢?PXI的信号包含了以下几种,其完整的架构如图三所示。

图二 典型3U高度的PXI系统架构。背板上的P1接插件上有32-bit PCI信号,P2接插件上则有64-bit PCI信号以及PXI特殊信号。那么前面所说的PXI特有的信号又是什么呢?PXI的信号包含了以下几种,其完整的架构如图三所示。  1. 10MHz参考时钟(10MHz reference clock) PXI 规格定义了一个低歪斜(low skew)的10MHz参考时钟。此参考时钟位于背板上,并且分布至每一个外设槽(peripheral slot),其特色是由时钟源(Clock source)开始至每一槽的布线长度都是等长的,因此每一外设槽所接受的clock都是同一相位的,这对多个仪器模块的同步来说是一个很方便的时钟来源。基本的10MHz参考时钟架构如图四所示。

1. 10MHz参考时钟(10MHz reference clock) PXI 规格定义了一个低歪斜(low skew)的10MHz参考时钟。此参考时钟位于背板上,并且分布至每一个外设槽(peripheral slot),其特色是由时钟源(Clock source)开始至每一槽的布线长度都是等长的,因此每一外设槽所接受的clock都是同一相位的,这对多个仪器模块的同步来说是一个很方便的时钟来源。基本的10MHz参考时钟架构如图四所示。  2. 局部总线(Local Bus) 在每一个外设槽上,PXI定义了局部总线以及连接其相邻的左方及右方外设槽,左方或右方局部总线各有13条,这个总线除了可以传送数字信号外,也允许传送模拟信号。比如说3号外设槽上有左方局部总线,可以与2号外设槽上的右方局部总线连接,而3号外设槽上的右方局部总线,则与4号外设槽上的左方总线连接。而外设槽3号上的左方局部总线与右方局部总线在背板上是不互相连接的,除非插在3号外设槽的仪器模块将这两方信号连接起来。局部总线架构如图五所示。

2. 局部总线(Local Bus) 在每一个外设槽上,PXI定义了局部总线以及连接其相邻的左方及右方外设槽,左方或右方局部总线各有13条,这个总线除了可以传送数字信号外,也允许传送模拟信号。比如说3号外设槽上有左方局部总线,可以与2号外设槽上的右方局部总线连接,而3号外设槽上的右方局部总线,则与4号外设槽上的左方总线连接。而外设槽3号上的左方局部总线与右方局部总线在背板上是不互相连接的,除非插在3号外设槽的仪器模块将这两方信号连接起来。局部总线架构如图五所示。  3局部总线(Local Bus) 在每一个外设槽上,PXI定义了局部总线以及连接其相邻的左方及右方外设槽,左方或右方局部总线各有13条,这个总线除了可以传送数字信号外,也允许传送模拟信号。比如说3号外设槽上有左方局部总线,可以与2号外设槽上的右方局部总线连接,而3号外设槽上的右方局部总线,则与4号外设槽上的左方总线连接。而外设槽3号上的左方局部总线与右方局部总线在背板上是不互相连接的,除非插在3号外设槽的仪器模块将这两方信号连接起来。局部总线架构如图五所示。

3局部总线(Local Bus) 在每一个外设槽上,PXI定义了局部总线以及连接其相邻的左方及右方外设槽,左方或右方局部总线各有13条,这个总线除了可以传送数字信号外,也允许传送模拟信号。比如说3号外设槽上有左方局部总线,可以与2号外设槽上的右方局部总线连接,而3号外设槽上的右方局部总线,则与4号外设槽上的左方总线连接。而外设槽3号上的左方局部总线与右方局部总线在背板上是不互相连接的,除非插在3号外设槽的仪器模块将这两方信号连接起来。局部总线架构如图五所示。  图六 PXI Star Trigger架构 4. 触发总线(Trigger Bus) 触发总线共有8条线,在背板上从系统槽(Slot 1)连接到其余的外设槽,为所有插在PXI背板上的仪器模块提供了一个共享的沟通管道。这个8-bit宽度的总线可以让多个仪器模块之间传送时钟信号、触发信号以及特订的传送协议。 PXI仪器模块的同步应用介绍 谈完PXI的特殊专有信号后,我们可以了解PXI系统只是提供了一个方便简洁的环境供用户使用,如何去运用这些信号,则必须与仪器模块搭配,才能真正发挥 PXI系统的优点。综观目前各家仪器模块厂商所能提供的PXI仪器模块,已经达到数百种可以选择,而不同种类的仪器也有不同的连接架构与方法。在此我们将以应用实例来说明如何利用PXI特有的信号,来达成同步的要求。 实例说明: 某种检测设备用来探测待测物体的结构,这种设备具有八个传感器,用来感应待测物体所传回的信息,并且以模拟信号送出其结果,其信号频率在7.5MHz左右。由于这八个信号互相有时间上的关系,因此当我们量测这八个传感器信号时必须要同一时间开始采集,并且采样时钟要同一相位,否则运算的结果会有误差。另外此检测设备在传感器开始传送信号时,同时会有数字触发信号输出,其数字与模拟信号关系如图七所示。

图六 PXI Star Trigger架构 4. 触发总线(Trigger Bus) 触发总线共有8条线,在背板上从系统槽(Slot 1)连接到其余的外设槽,为所有插在PXI背板上的仪器模块提供了一个共享的沟通管道。这个8-bit宽度的总线可以让多个仪器模块之间传送时钟信号、触发信号以及特订的传送协议。 PXI仪器模块的同步应用介绍 谈完PXI的特殊专有信号后,我们可以了解PXI系统只是提供了一个方便简洁的环境供用户使用,如何去运用这些信号,则必须与仪器模块搭配,才能真正发挥 PXI系统的优点。综观目前各家仪器模块厂商所能提供的PXI仪器模块,已经达到数百种可以选择,而不同种类的仪器也有不同的连接架构与方法。在此我们将以应用实例来说明如何利用PXI特有的信号,来达成同步的要求。 实例说明: 某种检测设备用来探测待测物体的结构,这种设备具有八个传感器,用来感应待测物体所传回的信息,并且以模拟信号送出其结果,其信号频率在7.5MHz左右。由于这八个信号互相有时间上的关系,因此当我们量测这八个传感器信号时必须要同一时间开始采集,并且采样时钟要同一相位,否则运算的结果会有误差。另外此检测设备在传感器开始传送信号时,同时会有数字触发信号输出,其数字与模拟信号关系如图七所示。  图七 检测设备的输出时序图 面对前述的量测需求,我们必须选择一个合适的量测模块,才能达到系统的要求。首先传感器所回传的信号频率为7.5MHz,因此根据奈氏采样定理,量测模块的采样频率必须在15MHz以上,且模块本身的输入频宽必须比7.5MHz高上许多,才不会造成输入信号的衰减。综观以上条件,我们选择凌华科技推出的PXI-9820作为量测模块。PXI-9820为一高速的数据采集模块,本身具有两个采样通道,其采样率高达65MS/s,前级模拟输入频宽高达30MHz。另外PXI-9820本身配有锁相环电路(PLL),可以对外界的参考时钟进行相位锁定。PXI-9820也可通过PXI的 Star Trigger,对其余13个外设槽传送高度精密的触发信号。因此PXI-9820十分适合用在这一个应用里。

图七 检测设备的输出时序图 面对前述的量测需求,我们必须选择一个合适的量测模块,才能达到系统的要求。首先传感器所回传的信号频率为7.5MHz,因此根据奈氏采样定理,量测模块的采样频率必须在15MHz以上,且模块本身的输入频宽必须比7.5MHz高上许多,才不会造成输入信号的衰减。综观以上条件,我们选择凌华科技推出的PXI-9820作为量测模块。PXI-9820为一高速的数据采集模块,本身具有两个采样通道,其采样率高达65MS/s,前级模拟输入频宽高达30MHz。另外PXI-9820本身配有锁相环电路(PLL),可以对外界的参考时钟进行相位锁定。PXI-9820也可通过PXI的 Star Trigger,对其余13个外设槽传送高度精密的触发信号。因此PXI-9820十分适合用在这一个应用里。  有了适合的量测模块之后,我们要开始规划如何进行量测。首先,由于共有八个传感器需要进行量测,而一个PXI-9820只有两个采样通道,因此我们需要四片 PXI-9820。其次量测规格要求各通道采样的相位要相同,因此每一张量测模块的时钟必须进行同步。由于每一片PXI-9820本身有板载采样时钟,因此其时钟无法保证都同相位。我们利用PXI背板所提供的10MHz参考时钟作为PXI-9820的外界参考时钟输入,利用PXI-9820本身的锁相回路电路进行时钟的相位锁定。图八是各片仪器模块的采样时钟不同步的情况。图九则为经过PLL锁相之后的时钟结果。

有了适合的量测模块之后,我们要开始规划如何进行量测。首先,由于共有八个传感器需要进行量测,而一个PXI-9820只有两个采样通道,因此我们需要四片 PXI-9820。其次量测规格要求各通道采样的相位要相同,因此每一张量测模块的时钟必须进行同步。由于每一片PXI-9820本身有板载采样时钟,因此其时钟无法保证都同相位。我们利用PXI背板所提供的10MHz参考时钟作为PXI-9820的外界参考时钟输入,利用PXI-9820本身的锁相回路电路进行时钟的相位锁定。图八是各片仪器模块的采样时钟不同步的情况。图九则为经过PLL锁相之后的时钟结果。

最后,由于检测设备在开始传送传感器的模拟数据时,会一并送出数字触发信号,我们将此触发信号当作每一片PXI-9820的触发条件。不过如何让这一个触发信号能精确的同时到达每一张PXI-9820呢?我们将其中一张PXI-9820插入Star Trigger Controller槽位,利用这一槽特有的Star trigger,传送给其余的三张PXI-9820以达到最精确的触发时间。 结论 利用PXI仪器模块与PXI平台作为量测与测试平台,不仅可以充分利用PCI的高速传输特性,以及继承用户原本就已熟悉的软件平台,更可以利用PXI所提供的触发信号来完成更精密的同步功能。全球各地的PXI开发厂商更为用户提供了数百种的量测测试仪器模块,让用户可以以最方便、快速及经济的方式完成适合本身应用的PXI系统。本文清楚的说明了PXI信号,并且以一简单的例子说明如何以PXI信号进行仪器模块之间的同步。希望能给予准备开发 PXI系统的用户一个初步的了解。

最后,由于检测设备在开始传送传感器的模拟数据时,会一并送出数字触发信号,我们将此触发信号当作每一片PXI-9820的触发条件。不过如何让这一个触发信号能精确的同时到达每一张PXI-9820呢?我们将其中一张PXI-9820插入Star Trigger Controller槽位,利用这一槽特有的Star trigger,传送给其余的三张PXI-9820以达到最精确的触发时间。 结论 利用PXI仪器模块与PXI平台作为量测与测试平台,不仅可以充分利用PCI的高速传输特性,以及继承用户原本就已熟悉的软件平台,更可以利用PXI所提供的触发信号来完成更精密的同步功能。全球各地的PXI开发厂商更为用户提供了数百种的量测测试仪器模块,让用户可以以最方便、快速及经济的方式完成适合本身应用的PXI系统。本文清楚的说明了PXI信号,并且以一简单的例子说明如何以PXI信号进行仪器模块之间的同步。希望能给予准备开发 PXI系统的用户一个初步的了解。

提交

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

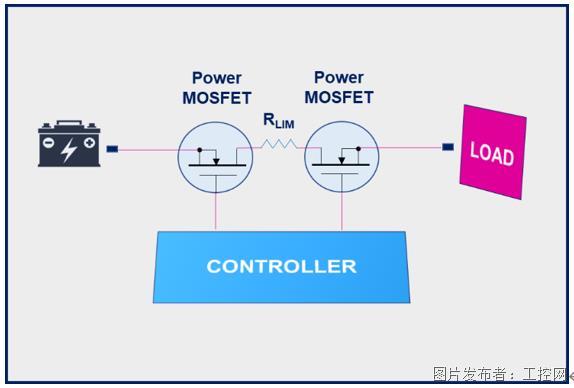

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议