PLC设计延时接通电路梯形图

2015/3/23 9:54:05

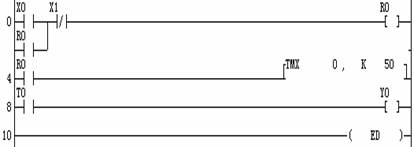

设计延时接通电路梯形图。控制要求时序如图4-37所示。输入端Ⅹ0、X1接不带自锁按钮,被控设备接于输出端子Y0。

例题分析:根据时序图设计梯形图,如图4-38所示。

图4-38 延时接通梯形图

当输入Ⅹ0端子的信号接通时,输入继电器的线圈Ⅹ0接通,其常开触点Ⅹ0闭合,内部继电器R0接通,其常开触点R0闭合,接通定时器T0,T0的设定值K50开始递减。减至“0”时T0的常开触点闭合,输出继电器Y0相对于X0延迟5s后接通。当输入端Ⅹ1接通后,内部继电器R0失电,R0的常开触点断开,定时器T0复位。T0的常开触点断开,使输出Y0为0FF。

提交

查看更多评论

其他资讯

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议