基于PCI总线的高速数据采集卡的设计

一、引言

数据采集是数字信号处理中的重要环节。针对不同任务,数据采集要达到的技术指标也不同。对于瞬态信号、雷达信号和图象处理都要求几MB/S甚至几十MB/S的速度。而目前用于PC机的数据采集卡大部分是基于ISA总线的,其最大缺点是传输速度太低,不能实现实时传输[1]。PCI总线是一种目前较为流行的、先进的高速同步总线,它的历史较短,正式的2.2版本于1999年2月发布。其优点在于能够实现设备间的快速访问,33MHZ/32位的PCI总线可以实现132MB/S的数据传输率,目前已经有66MHZ/64位的PCI总线,传输速率更快[2]。PCI是独立于处理器的同步总线,不需CPU的介入便可进行数据传输。此外,还支持突发传递、即插即用功能。PCI以其突出的性能备受计算机和通信界的青睐,将取代以往的总线,成为高档机及高性能工作站外设的基石。

二、数据采集卡的结构及性能

本数据采集卡主要由一个PCI总线控制器(PCI9050)[3],一块采集控制芯片(MAX7128),以及一个A/D转换模块构成,其具体的结构框图如图1所示。该数据采集卡的性能可以达到每秒采样20M个样本,A/D字长为8位,数据传输率在20MB/S以上,这对以往基于ISA总线的数据采集系统来说,根本无法实现。

图中粗线表示数据/地址总线,细线表示控制线。前端信号经过提取、放大后,进入A/D;在CPLD控制下,高速A/D芯片将模拟信号转为数字信号,并将数据输出,存储在双口RAM中;当一组数据存储完毕后,由CPLD通过PCI控制芯片向主机申请中断,主机响应中断后通过PCI控制芯片直接读取RAM中的数据。

三、数据采集卡的设计方案

1、PCI总线控制器的实现

由于PCI总线协议的复杂度较高,其接口电路实现起来相对困难。因此,目前主要有两种方案来实现PCI总线的控制:一种是采用专用的PCI接口芯片;另一种是用可嵌入PLD中的IP核。前者由于芯片本身已完成大部分PCI协议,不需设计者精通PCI协议的各种细节,开发周期短,但系统集成度较低,并且费用稍高;后者需要设计者根据PCI协议自己设计接口逻辑,要求设计人员完全掌握PCI协议,设计的难度相对较大,但由于可将PCI接口逻辑与用户逻辑集成在一片PLD中,提高了电路板的集成度和系统的性能。根据设计需求和实际情况,我们最终选择了第一种方式,采用了PLX公司的PLX9050作为PCI总线控制器,它即能满足设计需要,并且价格较低。

PLX9050是PLX公司推出的用于低成本适配器的PCI总线目标接口芯片,支持32位、33MHZ的PCI总线规范。它提供用于适配卡的小型而高性能的PCI总线目标接口,主要功能与性能如下:

(1)符合PCI2.1规范,接口芯片支持低成本从属适配器;

(2)五个本地总线地址空间和四个片选信号

(3)支持复用和非复用8位、16位和32位通用本地总线;

(4)串行EEPROM用于装载配置信息;

(5)可将两个来自本地总线的中断转换成PCI中断;

(6)支持本地总线与PCI总线时钟异步运行。

本设计方案采用了非复用方式(C模式),8位本地总线,两个地址空间,一个本地中断,接口电路的设计很简单,在此不作具体介绍。

如果不用PCI9050的默认配置(大多数情况不用),设计者需要对其进行配置。配置数据预先烧入EEPROM中,上电后PCI9050自动装入。PCI9050的配置寄存器分为两类。一类是PCI配置寄存器,另一类是本地配置寄存器。PCI配置寄存器配置PCI9050的PCI总线接口方面的属性,根据文档说明进行配置即可。本地配置寄存器配置PCI9050的本地总线接口的属性,由21个双字配置寄存器组成,要根据实际开发的硬件板卡的硬件资源进行配置。本地配置寄存器共分六类:本地地址空间范围寄存器(LASxRR)和扩展ROM范围寄存器、本地地址空间的本地基地址寄存器(重新映射寄存器LASxBA)、本地地址空间总线属性描述寄存器(LASxBRD)、片选基地址寄存器类(CSxBASE)、中断控制寄存器、混合控制寄存器。在编写配置EEPROM时,要注意各属性寄存器和控制寄存器的设置不要前后矛盾,地址范围和基址寄存器的设置要符合要求。在设计中,用了两个空间,一个为存贮器空间(对应双口RAM),一个为I/O空间(用于主机对采集卡的控制)。

下面以本地地址空间1为例说明将本地地址总线映射到PCI总线的过程。首先设置LAS3RR,初始化时PCI9050芯片将从EEPROM中读出此值,放入PCI基地址寄存器5中,主机先写入FFFFFFFFH后,再读回其值,为1的位表示需要分配地址。例如当LAS3RR的内容为FFF00000H时,PCI总线给本地地址空间3分配的PCI基地址可能是12300000H(此值是随机的)。该例中内存区域的大小是1M。接下来设置LAS3BA,即填入PCI地址12300000H对应的本地总线地址。例如若填入04000001H。表明PCI总线上对PCI地址12300000H的访问亦即对本地地址04000000H的访问(注意C模式时最多只有28条地址线,J模式时可以有32位)。然后设置对应的片选寄存器3,以便当PCI总线对本地总线地址空间3的地址进行访问时,片选信号3有效。其值设为04080001H,表示片选3的基地址是04080000H,其地址范围计算:基地址第一个不是零的位前面有19个零,则范围是2的19次幂再乘以2。这样当PCI的访问地址落入片选3寄存器定义的范围内时,片选3信号CS3#有效,用来选择本地总线上的外围设备。最后配置本地地址空间3的本地总线描述寄存器,具体请查看相应参考文档。

2、CPLD的内部逻辑设计

CPLD中集成了DMA控制器、PCI局部总线及A/D控制等功能,是设计中的重点。设计中选用ALTERA的EPM7128芯片,其内部逻辑框图如图2所示。其中,9050接口主要完成与PCI总线的握手,例如根据9050的时序要求产生相应的响应信号、当一组数据写入完毕后产生中断请求信号等;时钟部分用于产生片内各种时钟信号;控制部分主要根据主机命令开启(关闭)A/D及对CPLD片内其它部分进行控制;DMA控制器的关键部分是地址控制器,写入RAM时地址控制器根据A/D频率产生递增的RAM地址,另外还有RAM片选信号等其它必要的逻辑。

主机通过向本地I/O空间的特定地址单元写入特定值来发出启动命令,控制部分使A/D相应引脚置有效,以启动A/D。A/D数据线上数据有效的同时,DMA控制器输出RAM写地址和RAM片选信号,将数据存入RAM。当RAM地址大于特定值(此值小于RAM容量)时,PCI局部总线部分产生LINT信号,申请中断。同时,A/D仍继续按地址递增方式将变换后数据存入RAM,当RAM写地址为最高有效地址后,地址控制器归零,重新向RAM低地址写入数据。由于PCI总线速度比A/D变换速度快,不会出现未读数据被覆盖的情况。主机收到中断信号后,进入中断处理程序,从低地址开始读取数据采集卡上的RAM。PLX9050的数据线/地址线与RAM的数据线/地址线直接相连,读写控制线与CPLD相连,中断过程中,CPLD根据逻辑产生控制信号, PLX9050直接读RAM中的数据。

四、驱动程序的开发

在WINDOWS系统下,外设欲与主机进行数据交换,必须有自己的设备驱动程序。设备驱动程序的编写,也是对设计者要求较高的一部分[4]。现在比较流行的驱动开发工具有DDK、VtoolsD和WinDriver等,其中WinDriver是专门用于快速开发PCI/ISA设备的驱动程序开发组件。利用它开发设备驱动程序不需要熟悉操作系统的内核,整个驱动程序中的所有函数都是工作在用户模式下的,通过与WinDriver的.Vxd或.Sys文件交互来达到驱动硬件的目的。WinDriver的主要特征如下:

(1)提供了从用户层直接访问硬件的方法;

(2)无需DDK以及核心态驱动程序的开发经验;

(3)对主流的PCI接口芯片(PLX、AMCC、V3系列)提供了很好的支持;

(4)支持I/O、DMA、中断处理,支持PCI、ISA、USB、PCMCIA的开发;

(5)对于性能要求特别苛刻的部分通过WinDriver提供的API插入到核心态模式运行,以提高执行效率。

(6)可利用常见的软件开发平台(Visual C++、Borland C++、Delphi等);

有两种利用WinDriver开发驱动程序的方法,现分别介绍如下:

(1)利用WinDriver自带的WinDriver Wizard分析用户开发的插卡,看其是否像设计的那样正常工作,然后自动生成驱动程序的框架代码 ,修改代码并加入定制功能,在用户态执行和调试代码并将性能要求苛刻的部分插入到核心态。

(2)另一种方法是直接应用WinDriver提供的API函数来编写驱动程序,实践证明这种方法比用Wizard生成框架代码的方法更灵活方便。但要求编程人员对驱动程序的框架有一定的了解。 一般来说,驱动程序的结构如下所示:

a、打开WinDriver设备;

b、查找要访问的PCI设备;

c、枚举该设备的资源(内存、I/O、中断);

d、锁定该设备的资源;

e、访问插卡上的资源(读写内存、读写I/O、响应中断);

f、解锁资源;

g、关闭WinDriver设备。

本设计中主要用到中断调用。在用户态,理论上WinDriver能够处理每秒两万次的中断,若所用RAM为1K,则最高数据传输速率为20M/B。实际上,中断处理速度达不到2万次/秒,可考虑增加RAM容量以提高传输速度。也可以考虑将速率要求高的部分插入到核心态运行。

以下是一段使用WinDriver开发的PLX9050的驱动代码,从中可以看出WinDriver驱动程序的框架结构,只要对其稍作修改就可作为其他PCI卡的一部分。程序中没有给出变量说明,具体说明请查阅WinDriver的设计文档。

hWD=WD_open();//打开WinDriver设备,得到一个文件句柄; Pciscan..searchId.dwVenderId=0x10b5;//PLX公司供货号; Pciscan..searchId.dwDeviceId=0x9050;//PXL9050的设备号; WD_PCIScanCards(hWD,&Pciscan)//检测PCI插槽上的设备; PciSlot=Pciscan.cardslot[0];//将插卡的地址传递给变量PCICardInfo来 PCICardInfo.pcislot=PciSlot;//检测卡上的资源信息; WD_PciGetCardInfo(hWD,&PciCardInfo);//检测卡上的资源信息; Card=PciCardInfo.card; Cardreg.card=Card; WD_CardRegister(hWD,&Cardreg);//向系统登记检测到的资源信息; Item=Card.Item[0];//将卡上的0号资源赋给变量Item; If (Item.item==ITEM_MEMORY) RegAddress=Item.I.Mem.dwTrans.Addr;//得到PCI卡上的内存映射到用户态的地址; Trans.dwport=RegAddress; Trans.CmdTrans=RM_B;//设为内存字节读命令; Trans.fAutoinc=True; WD_Transfer(hWD,&Trans)//进行数据传递; WD_CardUnregister(hWD,&Cardreg)//释放注册到的资源; WD_Close(hWD)//关闭WinDriver设备

五、结束语

现在A/D芯片的采样速率可达几百兆次/秒,数据采集的速度取决于与计算机的接口和设备驱动程序的编写。虽然PCI9050具有简单的用户接口和低廉的价格,不失为低成本PCI接口控制芯片的较佳选择,但仍会成为超高速数据采集卡瓶颈。PCI9030是PLX公司最新推出的PCI芯片,与PCI9050具有相似的结构,支持高达66MHZ的局部总线时钟,将能满足超高速的需要。利用Windriver编写的设备驱动,不是真正的核心态程序,效率不是太高,对于超高速外设,可以考虑用微软的DDK编写高效的核心态程序。总之,利用PCI总线的高速特性实时传输和存贮采集数据,有效的解决了数据传输和处理的实时性。PCI总线可以满足从高速到超高速不同等级数据采集卡的需要,基于PCI总线的数据采集系统有很大的发展空间,十分广阔的前景。

提交

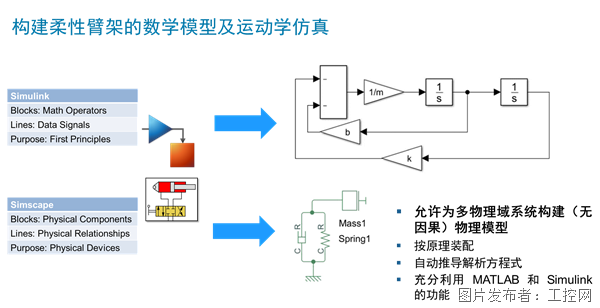

超越传统直觉,MATLAB/Simulink助力重型机械的智能化转型

新大陆自动识别精彩亮相2024华南国际工业博览会

派拓网络被Forrester评为XDR领域领导者

智能工控,存储强基 | 海康威视带来精彩主题演讲

展会|Lubeworks路博流体供料系统精彩亮相AMTS展会

投诉建议

投诉建议