基于CompactPCI总线数字隔离I/O模块的实现

1、引言 PCI总线一个重要的特点是其具有极高的数据传输速度,是新一代微机的标准总线,但是PCI的金手指插卡方式不能满足工业的高机械强度要求。CompactPCI规范是由PICMG制定的,在电气、逻辑和软件功能方面与PCI标准完全兼容(PCI规范请详见参考文献1),它制定了机械结构上更加坚固耐用的PCI版本,用于工业和嵌入式应用,是一种新的开放的工业计算机标准。本文介绍的基于CompactPCI总线的数字隔离I/O模块是应用于对抗震性能要求较高的内场测试系统上。 2、CompactPCI总线接口的设计 目前CompactPCI接口卡的设计一般有两种方法,第一种是基于将PCI接口完全集成到ASIC中,这样做的好处是集成度高,量产的生产成本低,直接用成熟的核。另一种方法可以根据CompactPCI协议在FPGA中实现CompactPCI总线接口控制器,但是由于CompactPCI总线协议自身的复杂性,要想在短期内做到操作稳定,难度很大。综合项目需求、成本、开发难易及后续开发等几个问题考虑,选择了PLX9030芯片作为设计基于CompactPCI总线的接口芯片。

图1PLX9030控制原理示意图 图1PLX9030控制原理示意图

2.1、PLX9030实现CompactPCI总线接口设计 如图2所示,设计主要由三个功能部分组成:一个是PLX9030与CompactPCI总线的接口控制逻辑,一个是它与局部总线的接口控制逻辑,还有一个即是与CompactPCI配置存储器串行EEPROM的接口控制逻辑。

图2PLX9030实现CompactPCI总线接口控制 图2PLX9030实现CompactPCI总线接口控制

PLX9030接口控制芯片把CompactPCI总线和局域总线连接起来,把所有的CompactPCI接口信号做在芯片内部。本模块局域总线控制单元,用于输入输出选通控制,应用简单译码、琐存和缓冲,最终实现可分别一一控制的16位数据输入和16位数据输出,控制原理比较简单,为了节约板卡空间,用CPLD7128完成。设计方法请详见参考文献3。CompactPCI配置存储器串行EEPROM的接口控制逻辑是设计中的重点。

2.2配置寄存器 PCI规范规定任何PCI设备必须实现一定数目的配置寄存器,以提供必要的配置信息。9030对应的串行EEPROM容量需大于2Kbit(128words*16bit),并且需要有地址自增功能,在该课题中选用了93LC66芯片。PLX9030提供了与串行EEPROM管脚—一对应的接口,只需对应连接即可,如图2。需要配置的寄存器请详见参考文献2。 上电过程中,PLX9030的内部寄存器由PCIBUS的RST#信号复位,并给出响应信号RETRY,在LOCALBUS上输出LRESET#信号,检查串行EEPROM是否存在。如果安装了EEPROM,PLX9030开始读串行EEPROM,若读出的第一个字非FFFFH,则PLX9030继续读操作,PLX9030用EEPROM中的值来配置片内的寄存器,否则认为EEPROM无效使用缺省值。对PLX9030来讲,EEPROM的前四个字节应该是30H、90H、B5H、10H,其中9030H为设备号,10B5H为厂商号。则PLX930用EEPROM中的值来配置片内的寄存器,否则使用缺省值。 3、模块隔离电路的设计 隔离是指使用变压器、光电或电容耦合等方法在被测系统与测试系统之间传递信号,避免了直接的电气或物理连接。光电耦合器以光电转换原理传输信息,它不仅使信息发出端(一次侧)与信息接收端(二次侧)是电绝缘的,从而对地电位差干扰有很强的抑制能力,而且有很强的抑制电磁干扰的能力,且速度高,价格低,接口简单,因而得到广泛的应用。 光电耦合器的一次侧都是发光二极管,但是二次侧有很多种结构,如光敏二极管、光敏晶体等,本卡选用光电耦合器的是高速CMOS型的,传输率可达10MHZ,型号为HCPL2630,原理说明请详见参考文献4。它的一次侧与二次侧的延迟时间只有28ns,因此速度远远超过普通光电三极管型的光电隔离管。内部结构原理图如3。加装光电隔离电路的方法如图4。

图3HCPL2630内部原理 图3HCPL2630内部原理

图4光电耦合器的连接图 图4光电耦合器的连接图

由于光电耦合器的前端是发光二极管,最大电流不能超过15mA,因此一定要加上限流电阻R。限流电阻R的阻值的大小,对光电耦合器的性能影响很大。R过大,会导致脉冲边缘延迟较大,R过太小,又很容易使光电耦合器前端发光二极管损坏而缩短光耦寿命。因此需要经过多次反复的实践才能最后确定。由于器件有个体的差异,在调试过程中,也遇到个别的光电耦合器在运行一段时间后才发现驱动能力不够,需要减小限流电阻、增大电流才能使发光二极管可靠导通的情况。 光电耦合器输入端和输出端供电要使用不同电源,于是在板卡上应用了DC5V—DC5V电源隔离模块,自带∏型滤波器,在增加少量的外加电路后能达到很小的输出纹波。 4、模块的硬件原理 如图5,当数字信号从CompactPCI的J2连接器输入到数字隔离I/O模块时,首先经过了光耦隔离器,保证了外部的信号不对板上其他信号造成电压冲击;当总线发出读操作命令时,PLX9030、CPLD接收了读操作命令,相应的控制位把隔离后的信号送给CompactPCI总线。

图5数字隔离I/O模块硬件原理 图5数字隔离I/O模块硬件原理

当数字信号从CompactPCI总线向局部总线输出时,首先通过PLX9030把相应的控制位和数据送到CPLD中,CPLD接受了命令后,把相应的数据经光耦隔离器及驱动器送出。外部设备可以通过CompactPCIJ2自定义针脚根据需要进行控制。 5、WinDriver开发设备驱动程序 (1)打开WinDriver应用程序后,出现DriverWizard,选择创建新Driver,出现当前系统中所有的硬件卡的列表,如图6所示。

图6当前系统中所有的硬件卡的列表 图6当前系统中所有的硬件卡的列表

从列表中选择需要建立驱动程序的硬件设备,对于PCI设备,点击Generate.INF按钮建立安装信息文件1518.inf。然后对1518.inf中的部分内容按照板卡所需信息进行修改。 (2)用DriverWizard生成操作硬件的应用程序级API函数。存放于DIO.h文件中。 (3)启动VC++6,建立一个DLL工程,将Wizard产生的部分单元文件包含进工程中,在此基础上加入完成特定任务的代码,利用DIO.h中的API函数,完成DIO.c,并提供应用程序的调用接口。 (4)编写接口单元文件DIO.def,将工程编译成动态链接库DIO.dll。应用程序就可以直接调用此动态链接库。在主测试程序中调用DIO.dll动态链接库,操纵数字隔离I/O模块配合其它模块运行。 6、运行结果及讨论 至今为止,基于本方案的数字隔离I/O模块已经成功地应用于内场测试系统中并实现量产。数字隔离I/O模块是CompactPCI结构的内场综合测试系统的重要模块之一,能够同时实现数字信号输入和输出两大模块的功能,简化了外围硬件的选择,也提高了系统的通用性和可扩展性;同时对输入输出采取了光电隔离措施,使系统同外部设备之间实现了电绝缘,整个系统的抗干扰性能大大提高。该模块的设计具有通用性,可以应用到其它CompactPCI总线的系统中,随着CompactPCI总线在军事工业领域的应用不断增多,有广阔的发展应用前景。 本文作者创新点:数字隔离I/O模块实现了数字信号输入和输出两大模块的功能,简化了外围硬件的选择,提高了系统的通用性和可扩展性;同时对输入输出采取了光电隔离措施,使系统同外部设备之间实现了电绝缘,整个系统的抗干扰性能大大提高。 |

提交

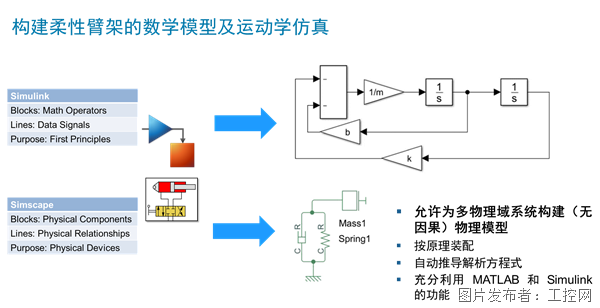

超越传统直觉,MATLAB/Simulink助力重型机械的智能化转型

新大陆自动识别精彩亮相2024华南国际工业博览会

派拓网络被Forrester评为XDR领域领导者

智能工控,存储强基 | 海康威视带来精彩主题演讲

展会|Lubeworks路博流体供料系统精彩亮相AMTS展会

投诉建议

投诉建议