硬件电路设计丨基于PXI总线宽带变频率计设计

1测频简述

频率信号具有抗干扰性强,易于传输,易于保持信息完整性和可以获得较高测量精度等优点,被广泛应用于日常生活、工业等各个领域,频率测量成为信息提取、设备检测等过程中的一个重要环节。频率检测作为电子测量领域最基本的测量之一,随着数字电子技术的发展而得到了长足的进步,数字频率测量也得到了越来越广泛的应用,从而使测频原理和测频方法的研究受到越来越多的关注。

2硬件电路设计

2.1信号调理电路设计

被测信号为1Hz~6GHz,频带范围较宽,而CPLD/FPGA中计数器工作频率不超过200MHz,因此需要对被测信号进行预处理。该频率计模块包含3个测试通道,分别为0,1,2通道。其中,O通道所测频率范围为1~6GHz;1通道所测频率范围为50MHz~1GHz;2通道所测频率范围为1Hz~50MHz。对于0,1通道的信号,由于频率较高,因而先由高频信号接收器进行接收整形,然后经前端分频器分频后送到FPGA/CP-LD进行计数;对于2通道所测的信号被放大整形后直接送到FPGA/CPLD计数。

2.2器件选择

由于该频率计模块分3个测试通道,对应不同的测试通道,选用了相对应的器件。在O通道,选用Zarlink公司的ZL40800和SP8782,实现8×32分频;在1通道,选用SP8782实现32分频;在2通道选用施密特触发器对信号进行放大整形。高稳定度晶振选用TC75温度补偿晶振,其稳定度为±10-8;FPGA选用Altera公司的EPM7032SLC44-5,其速度等级为5ns,既满足了该电路的要求,又兼顾了电磁兼容;高频信号接收器采用NB6L16差分接收器,其接收的最高信号频率可达6GHz。

2.3PXI总线接口电路设计

专用PCI接口芯片加CPLD/FPGA的接口方案,采用专用接口芯片PCI9030虽没有像直接采用CPLD/FPGA那么灵活,但它可以大大缩短开发周期,并且专用总线接口芯片具有通用性,提供配置寄存器,具备用于突发传输功能的片内FIFO等优点,避免了自行设计PXI总线将大量的人力和物力投入到纷繁的逻辑验证、时序分析工作上,开发周期长的弊端。

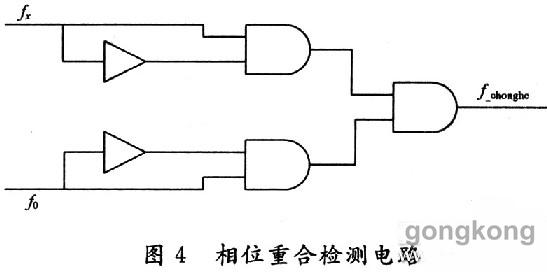

2.4基于FPGA的相位重合检测电路设计

相位重合检测电路基本原理:利用FPGA内部的延时特性,信号经过方向延时后和原信号相与,即可获得与延时时间长度相同的输出,且输出间隔为各自的周期,当两路信号在第一次与门之后重合时,y输出高电平,此时判断两信号相位重合。EPM7032SLCA4-5的延时时间为5ns。电路图如图4所示,时序图如图5所示。

3基于PXI总线的宽带频率计设计

3.1PXI总线介绍

PXI总线是在PCI总线内核技术上增加了成熟的技术规范和要求形成的。它通过增加用于多板同步的触发总线和参考时钟(10MHz),用于进行精确定时的星型触发纵向,以及用于相邻模块间高速通信的局部总线来满足用户试验和测量的要求。PXI将Windows95和WindowsNT定义为其标准软件框架,并要求所有的仪器模块都带有按VISA规范编写的WIN32设备驱动程序,使PXI成为一种系统级的规范,确保系统易于集成和使用。

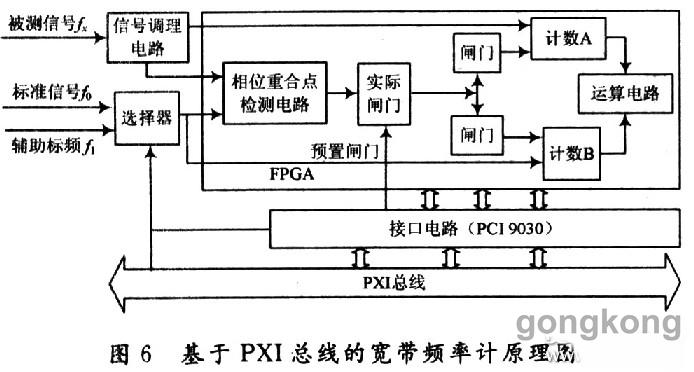

3.2频率计系统组成

被被测信号经过调理电路预处理后与标准频率一起输出到相位检测电路后,由总线控制打开预制闸门,当检测到相位重合时,实际闸门开启并计数,当预制闸门下降沿到来时并不立即停止计数,而是等到下一次的脉冲重合点到来时关闭闸门并停止计数,系统由PXI总线进行控制。原理图如图6所示。

提交

新大陆自动识别精彩亮相2024华南国际工业博览会

派拓网络被Forrester评为XDR领域领导者

智能工控,存储强基 | 海康威视带来精彩主题演讲

展会|Lubeworks路博流体供料系统精彩亮相AMTS展会

中国联通首个量子通信产品“量子密信”亮相!

投诉建议

投诉建议