HDLC通信卡如何满足高速数据传输的需要?

PCI总线及在其基础上发展起来的CPCI总线,在工业控制、数据采集、信息通信、航空航天等领域得到了广泛的应用。高级数据链路控制(HDLC)是一个在同步网上传输数据并面向位的数据链路层协议,具有透明传输、高可靠性、高传输效率以及高灵活性等特点,可以实现点到点或者点到多点的数据传输,在路由器、网关等通信或者网络设备中应用广泛。为了满足实际工作的需要,并为后续系统升级提供拓展空间.

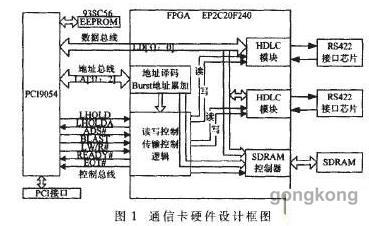

1 HDLC通信卡总体方案

通信卡主要采用PCI9054和FPGA构成硬件系统,其硬件结构如图1所示。数据传输流程为:接收数据时,通过RS一422接口芯片接收数据,数据格式满足简化的HDLC协议;通过FPGA内部的HDI.C模块进行数据接收和串并转换;然后在本地控制逻辑的控制下通过PCI9054以DMA方式传给上位机,实现数据的接收和判读;发送数据时,上位机软件将数据以DMA方式传给PCI9054再输入FPGA,在其内部HDLC模块的作用下,进行数据并串转换和HDLC协议转换,最后通过RS一422发送器进行电平转换和数据发送。预留SDRAM以满足大容量数据通信需要。

2 HDLC通信卡电路设计

2.1 总线接口设计

PCI总线具有性能高、成本低、良好开放性、良好兼容性等优点,但PCI总线具有严格的时序关系和电气规范,使得开发工作量和难度比较大。PCI总线一般都采用各IC生产商设计的PCI专用接口芯片进行PCI总线设的开发,以减少开发困难、降低工作量。基于此考虑,在本设计中,采用PLX公司的PCI9054芯片进行总线开发。

PCI9054芯片满足PCI V2.2协议,可作为桥接芯片在PCI总线和本地总线(10cal bus)之间提供信息传输,既可以作为两个总线的主控设备去控制总线,也可以作为两个总线的目标设备去响应总线。其本地总线可工作在M、C、J三种模式,可方便地与多种微处理器连接。在C模式下,因本地总线的地址线和数据线分开,时序与控制逻辑比较简单,得到了广泛应用。因此本通信卡中,PCI9054工作于C模式从设备方式,本地总线时钟采用40 MHz恒温补偿晶振。PCt9054的PCI总线端引脚按照对应关系与PCI总线金手指连接器相连,本地端地址总线为15 bit,数据总线为32 bit,控制总线包括ADS、BLAST、LHOLD、LHOLDA、LW/R#、READY、EOT#引脚,将它们分别与FPGA的10口互连。

2.2 FPGA芯片选型与设计

HDLC协议是面向比特的高级数据链路控制规程,具有强大的差错检测功能、高效和同步传输的特点,利用它可以确保数据信息可靠互通。市场上有许多使用简单的专用HDLC芯片,但由于HDLC标准的文本较多,这些芯片出于专用目的难以通用于不同版本,缺乏应用灵活性,且其片内存储器容量有限。另一种方法是通过软件对MCU编程实现HDLC协议,虽然功能灵活、适应性强,但处理速度慢、占用处理器资源多,难以高速实现对HDLC数据的插“0”和去“0”操作,一般只适用于路数较少的低速场合141。

为了实现与当前系统HDLC协议的兼容,本通信卡采用FPGA实现HDLC收发功能模块,充分利用FPGA硬件可编程的特点,发挥其速度快、灵活性高、并行处理信号、实时性能够预测的优势。同时,考虑到通信卡传输一帧数据的长度通常为512 KB~1 KB,而PCI9054的DMA只有32长字FIFO,且PCI读写速度与HDLC收发速度不一致,需要利用FIFO进行数据缓存,达到时序匹配的目的。为了提高系统集成度及其可靠性,采用FPGA内部存储单元实现FIFO功能。因此,综合考虑FPGA内部存储单元数量、10引脚数量等,选择Altera公司的EP2C20一F240用于功能模块开发。EP2C20F240为QFP封装,可用IO口142个,内部LE 18 752个,内部RAM为239 616 bit,可以满足系统开发需要。

2.3 差分接口设计

通信卡对外通信采用RS一422方式传输数据,传输频率最高为768 kHz。因此,选用MAXIM公司的RS一422发送器MAX3032E和接收器MAx3094E,其数据传输率最高分别可达20 Mb/s和10 Mb/s,满足数据高速传输需要。

3 HDLC通信卡逻辑设计

通信卡上的FPGA完成PCI9054本地总线数据读写时序逻辑的转换,实现HDLC收发模块和FIFO数据缓存功能。设计中采用VHDL硬件描述语言实现各功能模块,利用Ahera公司的集成开发环境Quartus II(11.0)完成相关的编译、调试、下载等开发工作。

3.1 本地总线数据读写模块

PCI9054工作于C模式从设备方式,采用分散/聚合(Scatter—Gather)DMA方式进行数据快速传输,以发挥其速度快的优势。根据PCI9054读写时序图可知,在C模式从设备方式下,FPGA读取PCI9054本地端ads_n和hlast_n的引脚状态,判断是单周期读写状态还是猝发读写状态,实现地址获取和数据读写,其状态机如图2所示。同时,在上位机读数据完毕后,如果读FI.FO为空则将EOT#引脚拉低,将数据传输结束信号上传,强行停止主机数据读操作。这就需要在DMA初始化过程中,设置DMAMODE寄存器的第14位为EOT#有效模式。

提交

新大陆自动识别精彩亮相2024华南国际工业博览会

派拓网络被Forrester评为XDR领域领导者

智能工控,存储强基 | 海康威视带来精彩主题演讲

展会|Lubeworks路博流体供料系统精彩亮相AMTS展会

中国联通首个量子通信产品“量子密信”亮相!

投诉建议

投诉建议