SPI协议下TMS320C6000 DSP芯片与C8051 FXXX单片机的通信

2006/5/23 9:08:00

关键词:McBSP;TMS320C6204;C8051F231;DSP;SPI 中图分类号:TP368.1 文献标识码:A The Communication Between TMS320C6000 DSP and CS051FXXX under SPI protocol WANG Liang, HUANG Hong-quan (College of Electrical Engineering, GuangXi University, Nanning, 530004, China) Abstract: The SPI protocol is introduced in this paper. There have configuration and the interface circuit between TMS320C6204 and C8051F231. And present corresponding procedures between the transmitter and receiver. Key words: McBSP; TMS320C6204; C8051F231; DSP; SPI 1 概述 TMS320C6000 DSP[1](数字信号处理)芯片是美国TI公司推出的定、浮点兼容的DSPs系列芯片,一般具有2到3个高速、全双工、多通道缓冲串行接口(McBSP),其方便的数据流控制可使其与大多数高速的同步串行外围设备接口。而51系列单片机中的C8051FXXX单片机是由Cygnal公司最新推出一种高性能的单片机,具有丰富的串行接口:如标准的全双工UART串行总线及MO TOROLA的SPI串行总线。因此,二者之间可以进行高速的串行通信。 SPIt2j(Serial Peripheral Interface——串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS。SPI接口的最大特点是由主设备时钟信号的出现与否来界定主/从设备间的通信。一旦检测到主设备时钟信号,数据开始传输,时钟信号无效后,传输结束。在这期间,要求从设备必须被使能(SS信号保持有效)。 本文以TI公司的DSP TMS320C6204作为从设备与Cygnal的C8051F231单片机作为主设备进行通信的为实例,介绍了将TMS320C6204 DSP的多通道缓冲串行口McBSP(Multi - channel Buffered Serial Port)配置为SPI模式,从而实现 DSP与单片处理器(带SPI总线接口)之间的高速通信设计方法,同时给出了实现方法的相应程序框图。 2 TMS320C6204 DSP的多通道缓冲串口 McBSP[3]。多通道缓冲串行口McBSP的功能是提供器件内外数据的串行交换。同以前的串口相比,McBSP串口具有相当大的灵活性。表1给出了有关 TMS320CA204的McBSP管脚说明。其中串口接收、发送时钟和同步帧信号既可由外部设备提供,又可由内部时钟发生器提供,从而大大的提高了通信的灵活性。

提交

查看更多评论

其他资讯

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

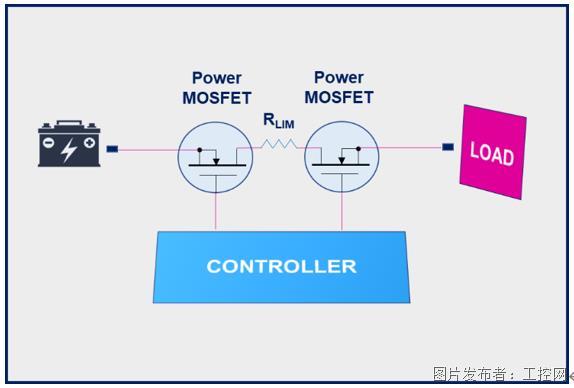

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议