计算机EPP控制CPLD显示点阵汉字的实现

1 引言

随着人们生活节奏的加快,越来越多的场合需要使用电子手段动态发布信息,其中应用非常广泛的一种方法就是LED点阵显示。传统的点阵汉字显示通常采用单片机作为控制核心,结合存储器、逻辑电路和LED点阵来实现。单片机具有良好的集成度,在很多对设备体积要求较高的场合得到了广泛应用。但是此方案开发和升级控制程序的工作量都很大[1]。在教学实践中对于学生软件方面的能力和协同工作锻炼有限。基于这些考虑,使用PC并口EPP模式控制CPLD的LED点阵显示方案具有较好的实用价值和易操作性。基于EPP的数据通讯系统比SPP和RS232具有更高的数据传输速率,适合于需要高速传输的场合[2]。本设计实际测试并证明了EPP模式下计算机并口与CPLD结合进行电子设计的可行性与高效性。实验中采用了16*16的LED点阵。

2 系统整体方案与协议

2.1 系统整体方案

本系统采用计算机并口以点阵的形式发送显示数据,CPLD作为系统数据处理核心来控制显示屏的驱动电路。待显示的文字全部使用计算机处理并生成点阵数据,因此可以选用无RAM的CPLD器件,同时也可以方便的直接控制显示效果,降低功耗。本系统采用ALTERA公司的EPM7128LS84-15。在设计中,将尽可能多的功能用计算机的软件来实现,以减少硬件的负担,并降低系统更新维护的代价。软件部分采用VC++6.0开发。

2.2 接口协议

本设计采用16*16的点阵显示器,每帧要求PC提供256路信号,显然对于PC并口来说,其I/O资源是不足的,需要CPLD来加以处理。计算机软件需要完成的工作有:①读取用户输入的文字,并将其转换为点阵数据;②定时使点阵循环移位,产生汉字移动的字幕效果;③定时以八位为单位发送当前需要显示的点阵,并发送若干控制信号,使CPLD控制LED显示相应的点阵,每帧需要发送32次。接口协议采用了3个控制位,以C0、C1和C2表示;CPLD返回的状态位与EPP的定义相同,在此不赘述。PC与CPLD之间的接口协议如下:

·CPLD上电给出在线信号Busy=1;

·PC检测Busy=1,发C0=1,C1=0,C2=0(通知CPLD:并口要开始发新帧的数据);

·CPLD应答nAck=1,并初始化内部地址变量Address=1111;

·PC检测状态nAck=1,发C0=0,C1=1,C2=0(通知CPLD:发送某一行的高8位数据),并发送高8位数据;

·PC发C0=0,C1=0,C2=0,确保高8位和低8位不会混淆;

·CPLD收到数据后,Address+1,高8位数据暂存,并发应答信号nSelect=1;

·PC检测nSelect=1,发C0=0,C1=0,C2=1(通知CPLD:发送同一行的低8位数据),并发送低8位数据;

·CPLD内部地址变量Address不变,把高8位数据与低8位数据组合成一行,发送显示数据,发送应答信号PaperEnd=1;

·PC检测PaperEnd=1,进入循环。

LED点阵显示采用逐行扫描,为了避免显示屏的闪烁,每秒至少需要刷新25次。系统整体框图见图1。

图1 系统整体框图

3 系统硬件设计

本设计中用到的显示屏是16*16点阵的,所以通过四个8*8LED点阵模块来组合成16*16点阵。图1中的行驱动器和列驱动器是必要的,因为CPLD输出的高电平可能不足以推动LED发光,造成点阵亮度不一的问题。实际设计中,采用反向器作为驱动。

在本设计中,CPLD是核心,有着承上启下的作用。因此,在接口协议确定的条件下,CPLD内部控制编写的VHDL程序的好坏关系到整个系统。根据前述协议可知,CPLD主要是完成与计算机的通信,再控制驱动电路使得LED点阵显示屏正常显示。本设计采用Max+PlusII编写VHDL程序,用Protel 99SE进行电路板设计。VHDL程序及注释如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity display is

port( clk: in std_logic;

c: in std_logic_vector(2 downto 0); --三位控制信号

data: in std_logic_vector(7 downto 0); --数据输入

status: out std_logic_vector(2 downto 0); --三位状态信号

col: out std_logic_vector(15 downto 0); --列输出

row: out std_logic_vector(15 downto 0) --行输出 );

end display;

architecture control of display is

signal v_row: std_logic_vector(15 downto 0); --暂存行数据

begin

row<=v_row; --输出行数据

process(clk,c,data)

variable address: std_logic_vector(3 downto 0); --行地址变量

variable hdata: std_logic_vector(7 downto 0); --暂存高八位列数据变量

variable t: std_logic; --局部变量控制“行地址加一”行为

begin

if clk'event and clk='1'then

if c="001" then

status<="110";

address:="1111";

t:='0'; --初始化变量

elsif c="010" then

status<="011";

if t='0' then --局部变量t=0行地址加一

address:=address+1;

t:= '1'; --行地址加一后立即置变量t为1

提交

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

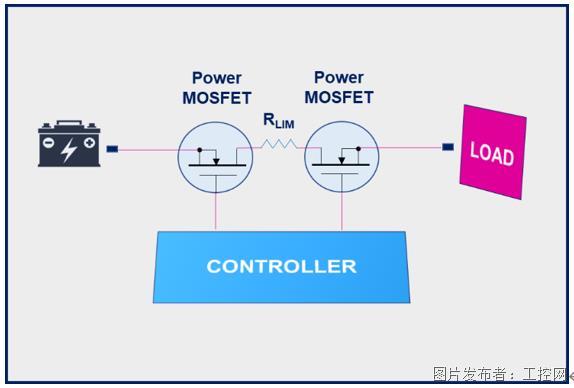

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议