基于FPGA和DSP的机载高清视频图像系统

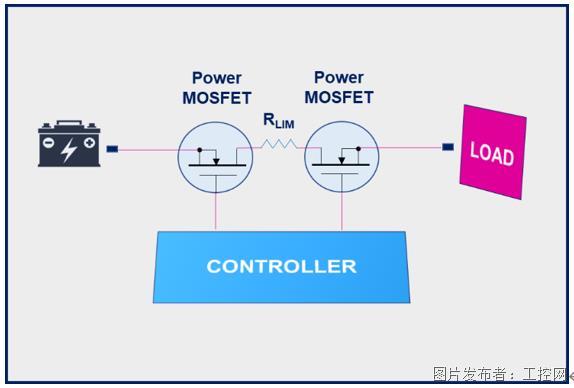

无人机广泛应用于军事侦察以及民用测绘等领域,其中的机载视频图像系统是机载电子系统中的重要环节之一。无人机在高空飞行中对地面景物摄像,所得图像帧内目标像素小且目标数量大,这要求增大图像分辨率以提高目标物体的辨识度。此时数据量随之显着增加,与有限的无线带宽资源成为矛盾,故要求应用高效的视频编解码技术。在侦察等特殊应用领域要求视频传输的实时性,此时需要保证实时的视频编解码以及较小的图像延迟。在需多路视频传输且总数据率固定的情况下,可通过降低单路视频分辨率或提高单路压缩比来实现,故系统应可动态切换分辨率和压缩比,具备较大的灵活性。无人机与地面的通信中,除了要回传视频数据以外,还要向地面传输飞行器本身的下行遥测数据,若采用两个独立信道会导致传输效率较低,此时设计一个包括传统遥测数据和视频数据的广义遥测系统成为必需。 本文设计并实现了一种基于FPGA和DSP的机载高清视频图像系统,包括机载设备端和地面站端两部分,最高支持分辨率为1 280� 720,每秒25帧的MPEG-4实时视频编解码,码速率在5 Mbps以下。并可通过上行遥控指令动态切换图像分辨率和视频码率,同时实现了视频数据与遥测数据的组帧传输。 本文首先对机载视频图像遥测系统进行概述,提出了系统的总体实现结构。然后具体给出系统的设计,分为硬件平台和程序算法两部分。硬件平台设计包括机载端视频采集、FPGA和DSP处理器和地面端CPCI总线接口的设计,程序算法设计包括视频编解码算法、机载端DSP程序和地面端上位机软件的设计。文章最后给出了系统挂飞实验的结果并作以总结。 1 系统概述 机载视频图像系统主要由机载设备端和地面站端两部分组成,系统总体结构图如图1所示。

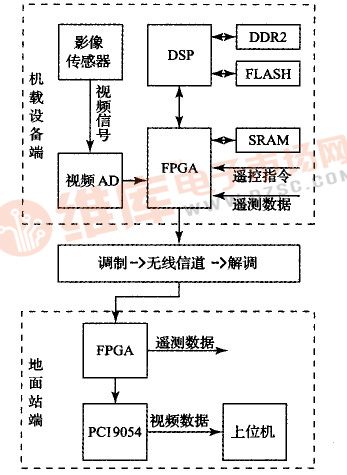

图1 系统总体 1)机载设备端 视频AD将影像传感器输出的高清视频模拟信号进行模数转换传递给FPGA,FPGA将预处理后的原始数字视频数据传递给DSP进行实时视频编码,DSP完成视频编码后将压缩码流回传给FPGA,在FPGA 中,压缩视频码流与下行遥测数据组帧后进入调制部分;同时上行遥控指令进入FPGA,对图像分辨率、视频码率进行控制。 2)地面站端 解调后的数据进入FPGA,FPGA将视频数据与遥测数据分离,其中遥测数据进入后续的分析处理,视频数据经PCI9054,通过CPCI接口上传给上位机,上位机完成对视频压缩码流的实时解码播放以及存储回放。 2 系统设计 2.1 硬件平台 2.1.1 机载端视频采集 高清模拟视频信号为保证信号质量,常采用分量输出格式,如亮度信号(Y)和色差信号(Cr、Cb)三分量输出,同时场同步和行同步信号可采取叠加在分量信号上的内同步方式输出。本系统中高清视频信号采用720 P(1 280�720)格式,25帧/秒,选用TI公司的视频ADC芯片TVP70025I完成该高清模拟视频的模数转换,采样精度及方式选取为8位,4:2:2(Y:Cb:Cr)采样。TVP70025I与外部器件连接关系如图2所示。TVP7OO25I输出数字化视频分量(Y、Cb和Cr)、数据时钟(DATACLK)、场同步(VS0UT)和行同步(HSOUT)信号给FPGA,DSP通过I C总线对TVP70025I内部寄存器进行初始化设置,并启动模数转换过程。

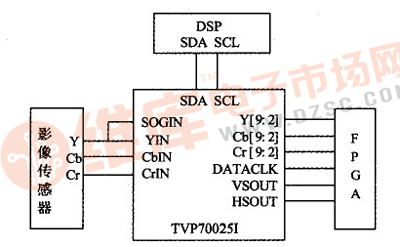

图2 TVP70025I硬件连接 2.1.2 机载端DSP FPGA处理器 机载端处理部分主要完成数字视频信号获取、视频压缩编码和遥控遥测接口功能,考虑到DSP强大的数字信号处理能力和FPGA 的大规模逻辑设计能力,系统采用FPGA DSP的硬件架构。 FPGA 选用Altera 公司STratixII 系列芯片EP2S30F672C5,该芯片有丰富的逻辑资源和嵌人式存储器,支持LVTTL、LVDS等接口电平标准。主要功能设计如图3所示。

图3 FPGA功能设计 包括以下3个方面: 1)数字视频获取 FPGA通过TVP70025I输出的场同步和行同步信号判断一场和一行视频的起始,接收原始视频数据(Y/Cb/Cr)并存人FPGA 内部开辟的FIFO之中,考虑到数据传输的高效性,需缓存若干行图像并一次性传递至DSP,由于FPGA内部存储器有限,故外挂SRAM 作为数据缓冲。 2)DSP与FPGA间数据传输 DSP与FPGA之间通过DSP的EMIFA 接口连接,FPGA内开辟FIFO 或者寄存器,DSP通过EMIFA读写FIFO或寄存器内的数据实现数据传输。本系统中分别开辟原始视频FIFO(Y/Cb/Cr 3个)、压缩视频FIFO和遥控指令寄存器,对应于DSP中的5个地址空间,以地址线的最高3位进行区分。考虑到最大数据吞吐率为原始视频的传递,EMIFA 数据宽度设为32位,数据时钟选取4O M Hz。 3)遥控及遥测 本系统中可接受地面测控站传递的上行遥控指令,通过改变采样方式,对视频分辨率进行切换,包括QCIF(176�144)、CIF(352�288)、标清(720�576)和高清(1 280�720)4种模式。同时可根据遥控指令改变编码算法中的参数,进而实现视频数据的码率控制,分为最高至最低5个码率等级。 编码后的视频数据与下行遥测数据进行组帧,作为整体码流进入调制阶段。系统中设计帧格式如表1所示。 表1 视频与遥测数据组帧格式

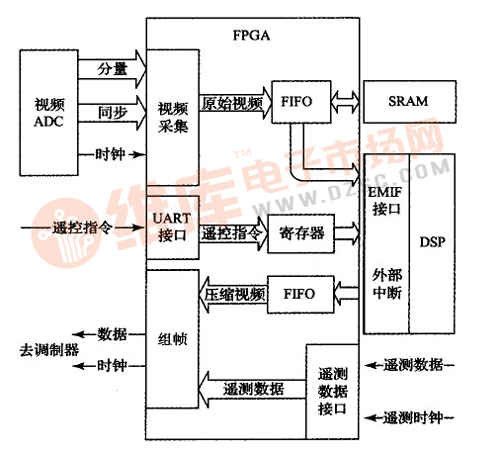

每大帧包括64个子帧,以1字节子帧计数标识,大帧计数以两字节时统信息标识。前63个子帧用于传输视频数据,考虑到采用变长视频编码算法后每帧压缩图像字节数不固定,组帧过程中需填充无效字节以保证每子帧中1 022字节的视频数据,故我们以两字节有效字节数来标识有效的视频字节数。第64子帧用于传输遥测数据。每个子帧以3字节同步码作为结束。 DSP选用TI公司的新一代高性能定点DSPTMS320C6455,它基于C64x 内核结构,片内采用L1/L2两级缓存结构,主频达1.2 GHz,最大峰值速度9 600 MIPS。 此外,TMS32OC6455拥有丰富的外部接口,如总线接口(FC等)和外部存储器接口(EMIFA、DDR2)等。主要功能设计如图4所示。

图4 DSP功能设计 DSP部分的设计主要为存储空间的分配,本系统中分配方式如表2所示。其中CE2空间主要用于与FPGA之间的数据交互,CE3空间主要用于代码的非易失性存储,CE0空间主要作为程序和数据运行的外部空问。表2 DSP存储空间分配

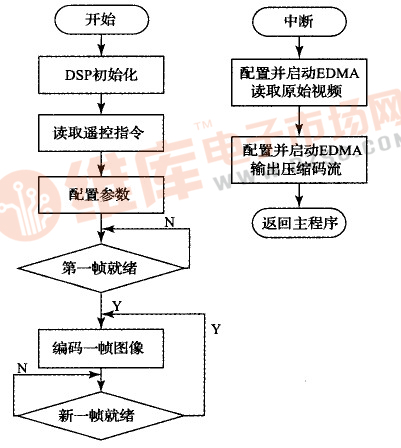

地面端采用FPGA PCI接口芯片的架构实现,其中,FPGA主要完成视频与遥测数据分离以及接口时序等功能,而PCI协议部分由接口芯片来实现,该种方式减小了FPGA的逻辑设计量。系统中FPGA选用Ahera公司CyclONe系列芯片EPIC12Q24oc8,PCI接口芯片选用PLX公司的PCI9054。PCI9054的PCI总线接口与CPCI插槽相连,本地总线接口与FPGA相连,EEPROM 用于加载配置数据。 2.2 程序算法 2.2.1 视频编解码算法 目前使用较多的视频编解码标准有国际标准化组织(ISO)与国际电工委员会(IEC)制定的MPEG一4标准,以及IS0和国际电信联盟(ITU)制定的H.264标准。相比MPEG一4标准,H.264的复杂度高,尤其对于高分辨率的应用,硬件实现难度很大,而MPEG一4以其实现复杂度低,同时适用于高低码率视频的特点,在嵌入式视频编解码系统中得到了广泛的应用。考虑到以上几点,本系统中选用MPEG一4标准作为视频编解码算法。 系统中选用开源的MPEG一4视频编解码器XVIDSimple Profile作为源代码。机载端完成视频编码功能。 将源代码去除用户交互等部分冗余代码后,完成向TMSC320C6455平台的移植。针对PC的XⅥD程序并不能满足实时编码的要求,需对程序进行优化:提高运行速度。首先对部分算法进行了优化,采用基于预测的运动估计 。其次进行代码优化:第一步利用CCS软件分析各部分代码的耗时,观察出效率较低的部分;第二步采取C语言级别的优化,如使用关键字、伪指令向编译器提供优化信息,使用内联函数,编写软件流水等;第三步选出第二步优化效果不明显的代码段,如量化/逆量化、1/2像素内插、运动补偿部分,用线性汇编改写。地面站端的上位机完成视频解码功能,经测试源代码即可满足视频解码的实时性。 2.2.2 机载端DSP程序 DSP程序分为主程序和中断程序两部分,其流程图如图5所示。系统上电或复位后,DSP开始运行主程序,首先完成DSP内部锁相环、EMIFA接口、DDR2接口、I C总线以及中断的初始化,此时DSP进入正常工作状态。然后通过EMIFA接口读取FPGA中的遥控指令寄存器,获取分辨率和视频码率信息。接下来根据获取的信息初始化MPEG-4编码算法的相应参数,对视频ADC进行配置并启动视频采集。FPGA在视频ADC启动后,每采集4行原始视频向DSP提出一次中断。DSP响应中断后,通过EMIFA读取4行原始视频,并输出1 264字节视频压缩码流。以高清(1 280�720)为例,需180次中断完成一帧图像的传递,且支持每帧图像压缩后最大为220 K字节。主程序判断新的一帧到来后,开始对这一帧进行编码。原始视频及压缩码流存储区均采用乒乓操作,与FPGA 的数据传递采用EDMA方式,故编码与数据传输互不影响,保证了实时性。

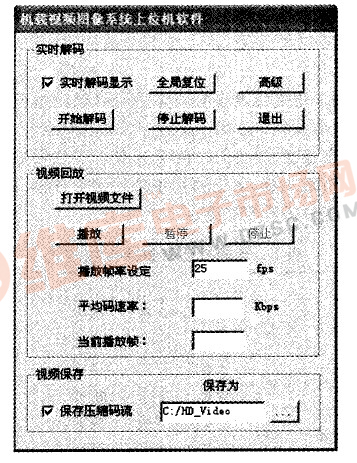

图5 DSP程序流程 2.2.3 地面端上位机软件 地面端上位机软件界面采用VC MFC编写,CPCI设备驱动程序采用Driver Studio编写,软件主要完成通过CPCI接口对视频压缩码流的读取、实时视频解码播放、视频文件保存回放等功能。软件操作简便、人机交互良好,界面如图6所示。

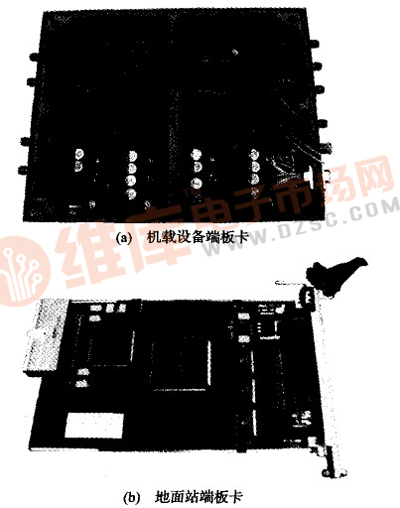

图6 上位机软件界面 3 实验结果 本文设计的机载高清视频图像系统设备体积小,功耗低,可靠性高,图7(a)、(b)分别为机载设备端板卡与地面站端板卡实物图。 图7 实物 本系统成功进行了有人机挂飞实验,共进行了两次实际飞行。每次的飞行测试时间为2 h,飞行高度为3 km,飞行半径为5 km,飞行速度在200 km/h左右。实验结果表明系统实现了分辨率为176�144、352�288、720�576和1 280�720,每秒25帧的MPEG-4实时视频编解码,同时支持视频码率控制,提供五个等级的视频质量的码流,平均码速率在5 Mbps以下。上位机解码后视频图像层次清晰,色彩饱满,系统带来的图像延迟小于500 ms,满足无人机侦察等领域的需求。不同分辨率及码率可通过遥控[1 ” 指令动态切换,同时遥测数据正确与视频数据组帧并分离,表明机载高清视频图像系统与遥控遥测系统得到了很好的融合。 4 结论 本文设计并实现了一种基于FPGA DSP的机载高清视频图像系统,包括机载设备端和地面站端两部分,具备以下特点: 1)最高支持720 P,每秒25帧的MPEG一4实时视频编解码,满足当今无人机对高分辨图像的需求; 2)视频分辨率及码率可通过遥控指令动态切换,视频与遥测数据组帧传输,实现与传统遥控遥测系统的融合; 3)设备体积小、功耗低、可靠性高,满足机载苛刻的环境要求。

提交

助力企业恢复“战斗状态”:MyMRO我的万物集·固安捷升级开工场景方案

车规MOSFET技术确保功率开关管的可靠性和强电流处理能力

未来十年, 化工企业应如何提高资源效率及减少运营中的碳足迹?

2023年制造业“开门红”,抢滩大湾区市场锁定DMP工博会

2023钢铁展洽会4月全新起航 将在日照触发更多商机

投诉建议

投诉建议