简述二进制解码器的作用和工作原理

解码器是一种组合电路,可将小比特值解码为大比特值。它通常与编码器结合使用,编码器的作用与解码器的作用完全相反,因此在继续使用解码器之前,请在此处阅读有关编码器的信息。同样,就像编码器一样,解码器也有多种类型,但解码器中的输出线数总是多于输入线数。在本教程中,我们将学习解码器的工作原理以及如何为我们的项目构建一个解码器。

解码器的基本原理:

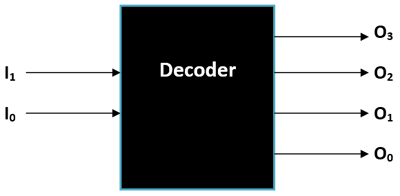

如前所述,解码器只是编码器的对应部分。它采用特定数量的二进制值作为输入,然后使用逻辑解码成更多行。下面显示了一个示例解码器,它将 2 行作为输入并将它们转换为 4 行。

解码器的另一个经验法则是,如果输入的数量被认为是 n(这里 n = 2),那么输出的数量将始终等于2 n(2 2 =4),在我们的例子中是 4。解码器有2条输入线和4条输出线;因此这种类型的解码器被称为 2:4 解码器。两个输入引脚命名为 I1 和 I0,四个输出引脚命名为 O0 到 O3,如上图所示。

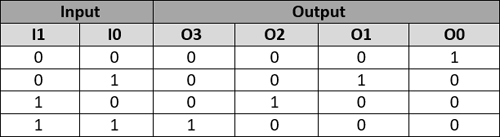

同样重要的是要知道,像此处所示的普通解码器具有无法区分两个输入为零(未连接到其他电路)和两个输入为低(逻辑 0)的条件的缺点。这个缺点可以使用优先解码器来解决,我们将在本文后面学习。一个普通解码器的真值表如下图

从解码器真值表中,我们可以为每个输出线编写布尔表达式,只需跟随输出变高的位置,并根据 I1 和 I0 的值形成 AND 逻辑。它与 Encoder 方法非常相似,但这里我们使用 AND 逻辑而不是 OR 逻辑。下面给出了所有四行的布尔表达式,其中符号 (.) 表示 AND 逻辑,符号 (') 表示 NOT Logic

O0 = I1’.I0’ O1 = I1’.I0 O2 = I1.I0’ O3 = I1.I0

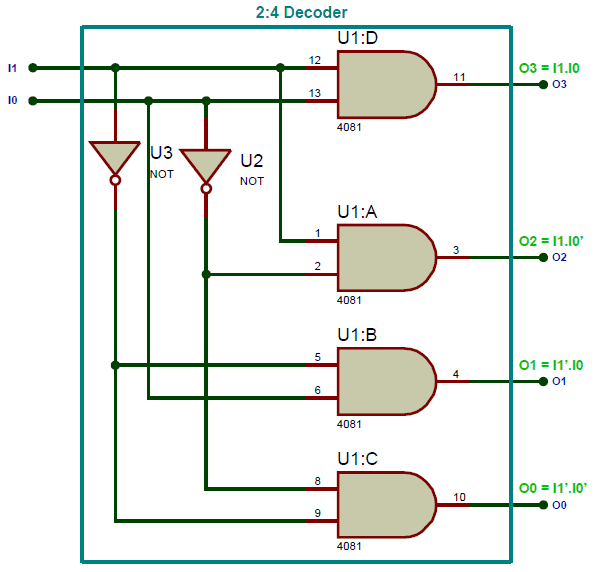

现在我们有了所有四个表达式,我们可以使用 AND 门和 NOT 门将这些表达式转换为组合逻辑门电路。只需使用 AND 门代替 (.) 和 NOT 门(反转逻辑)代替 ('),您将获得以下逻辑图。

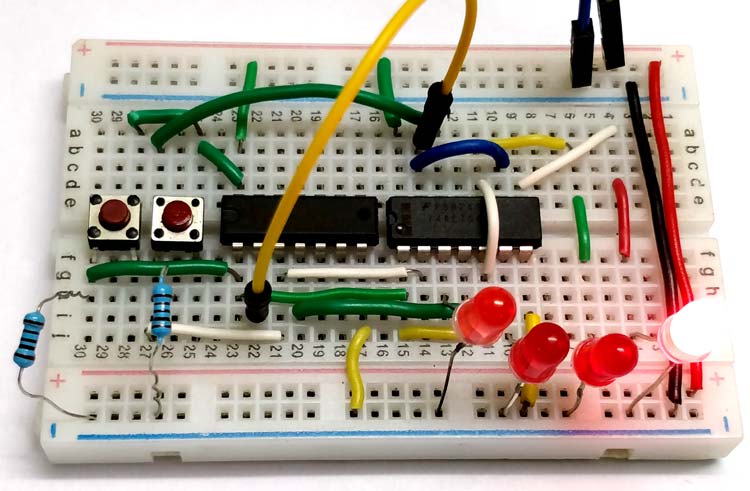

现在在面包板上构建2:4 解码器电路图,并检查它在现实生活中是如何工作的。要使其作为硬件工作,您必须使用逻辑门 IC,例如7404 用于 NOT 门,将7408 用于 AND 门。通过按钮提供两个输入 I0 和 I1,通过 LED 灯观察输出。一旦你在面包板上建立连接,它会如下图所示

该板由外部 +5V 电源供电,该电源反过来通过 Vcc(引脚 14)和接地(引脚 7)引脚为门 IC 供电。输入由按钮给出,按下时为逻辑 1,未按下时为逻辑 0,沿输入线还添加了一个值为 1k 的下拉电阻,以防止引脚处于浮动状态。输出线(O0 到 O3)通过这些红色 LED 灯给出,如果它们发光,则为逻辑 1,否则为逻辑 0。

请注意,每个输入的真值表显示在左上角,LED 也以相同的顺序发光。同样,我们也可以为所有类型的解码器创建组合逻辑图,并在这样的硬件上构建它们。如果您的项目适合,您还可以查看现成的解码器 IC。

标准解码器的缺点:

就像编码器一样,标准解码器也遇到同样的问题,如果两个输入都没有连接(逻辑 X),输出将不会保持为零。相反,解码器会将其视为逻辑 0,并且位 O0 将变为高电平。

优先解码器:

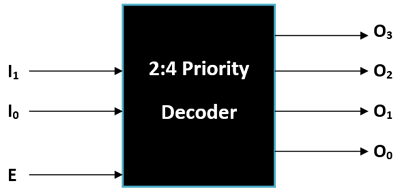

所以我们使用优先解码器来解决这个问题,这种类型的解码器有一个额外的输入引脚标记为“E”(启用),它将与优先解码器的有效引脚连接。优先解码器的框图如下所示。

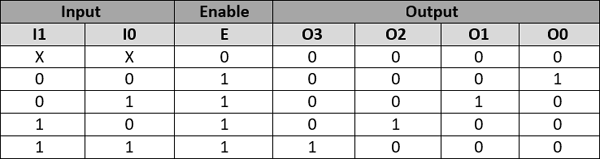

优先级编码器的真值表也如下所示,这里 X 表示无连接,“1”表示逻辑高电平,“0”表示逻辑低电平。请注意,当输入线上没有连接时,启用位为 0,因此输出线也将保持为零。这样我们就可以克服上面提到的缺点。

与往常一样,我们可以从真值表驱动输出线 O0 到 O3 的布尔表达式。上述真值表的布尔表达式如下所示。如果仔细观察,您会注意到该表达式与普通 2:4 解码器的表达式相同,但启用位 (E) 已与表达式进行了 AND 运算。

O0 = E.I1’.I0’ O1 = E.I1’.I0 O2 = E.I1.I0’ O3 = E.I1.I0

上述布尔表达式的组合逻辑图可以使用一对反相器(非门)和三输入与门来构建。只需将 (') 符号替换为反相器,将 (.) 符号替换为与门,您将得到以下逻辑图。

3:8 解码器:

还有一些更高阶的解码器,例如更常用的3:8 解码器和4:16 解码器。这些解码器通常用于 IC 封装中以提高电路的复杂性。将 2:4 解码器等低阶解码器组合成高阶解码器也很常见。例如,我们知道 2:4 解码器有 2 个输入(I0 和 I1)和 4 个输出(O0 到 O3),而 3:8 解码器有 3 个输入(I0 到 I2)和 8 个输出(O0 到 O7)。我们可以使用以下公式来计算形成像 3:8 解码器这样的高阶解码器所需的低阶解码器(2:4)的数量。

所需的低阶解码器数量 = m2/m1,其中,m2 -> 低阶解码器的输出数量 m1 -> 高阶解码器的输出数量

在我们的例子中,m1 的值为 4,m2 的值为 8,因此将这些值应用到上述公式中,我们得到

3:8解码器所需的2:4解码器数量=8/4=2

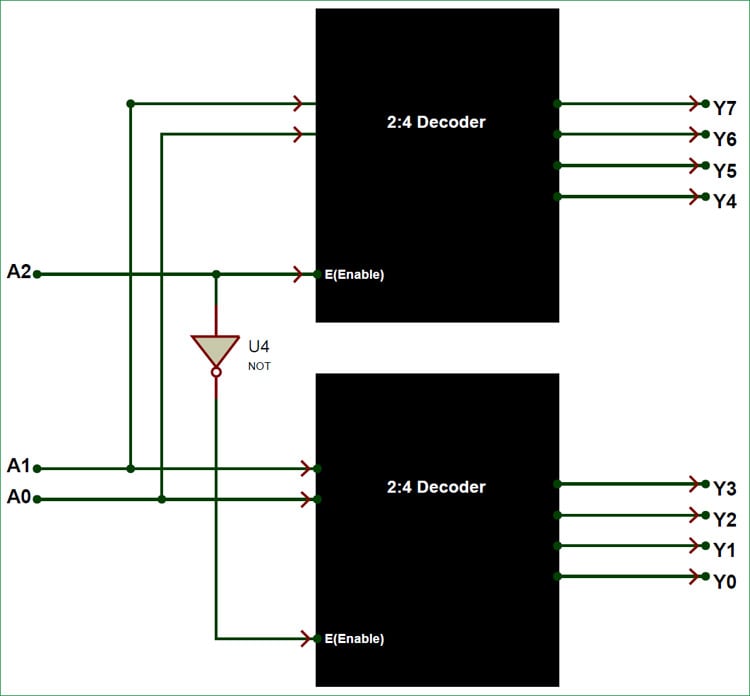

现在知道需要两个 2:4解码器来组成一个 3:8解码器,但是这两个应该如何连接才能聚集。下面的框图显示了

如上所示,输入 A0 和 A1 作为两个解码器的并行输入连接,然后第一个解码器的启用引脚用作 A2(第三个输入)。A2 的反相信号被提供给第二个解码器的使能引脚,以获得输出 Y0 到 Y3。这里输出 Y0 到 Y3 被称为低四个最小项,输出 Y4 到 Y7 被称为高四个最小项。从第二个解码器获得低阶最小项,从第一个解码器获得高阶最小项。尽管这种组合设计的一个明显缺点是,解码器没有启用引脚,这使得它容易受到我们之前讨论过的问题的影响。

4:16 解码器:

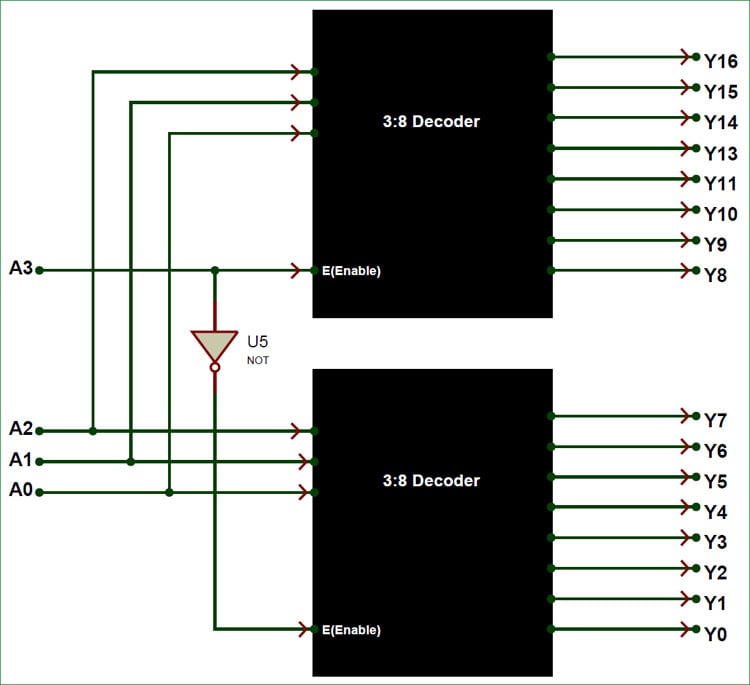

与 3:8 解码器类似,4: 16 解码器也可以通过组合两个 3:8 解码器来构建。对于 4:16 解码器,我们将有四个输入(A0 到 A3)和十六个输出(Y0 到 Y15)。而对于 3:8 解码器,我们将只有三个输入(A0 到 A2)。

我们已经使用公式计算了所需的解码器数量,在这种情况下,m1 的值为 8,因为 3:8 解码器有 8 个输出,m2 的值为 16,因为 4:16 解码器有 16 个输出,所以在我们得到的上述公式中应用这些值

4:16解码器所需的3:8解码器数量 = 16/8= 2

因此,我们需要两个 3:8 解码器来构建一个 4:16 解码器,这两个 3:8 解码器的布置也将与我们之前所做的类似。将这两个 3:8 解码器连接在一起的框图如下所示。

这里输出 Y0 到 Y7 被认为是较低的八个最小项,而从 Y8 到 Y16 的输出被认为是较高的八个最小项。右下方的最小项是使用输入 A0、A1 和 A2 直接创建的。第一个解码器的三个输入也提供相同的信号,但第一个解码器的启用引脚用作第四个输入引脚 (A3)。第四输入 A3 的反相信号被提供给第二个解码器的使能引脚。第一个解码器输出较高的八个最小项值。

应用:

解码器通常与编码器结合使用,因此它们都共享相同的应用程序。如果没有解码器和编码器,就不可能有现代电子产品,如手机和笔记本电脑。下面列出了解码器的几个重要应用。

测序信号应用

定时信号应用

网络线路

记忆元素

电话网络

本文由ID先生网www.mrchip.cn/category/编辑整理,请勿转载。图片来源网络,如有侵权,请联系删除。

提交

如何选择最好的 PCB 设计软件

罩极感应电动机的构造和工作原理

半减法器电路及其构造原理

使用运算放大器的仪表放大器电路

什么是直流发电机? 直流发电机的种类

投诉建议

投诉建议